- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Re: DDR Memory Map default config value for TZASC

DDR Memory Map default config value for TZASC

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

DDR Memory Map default config value for TZASC

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear NXP team.

I have a question about DDR Memory Map default config.

I got the answer from the bellow link.

DDR Memory Map default config value for TZASC

But

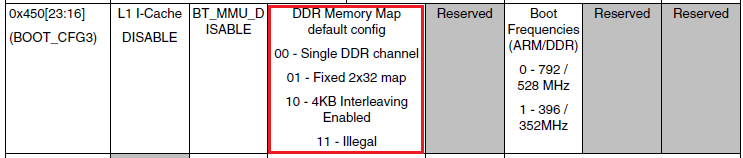

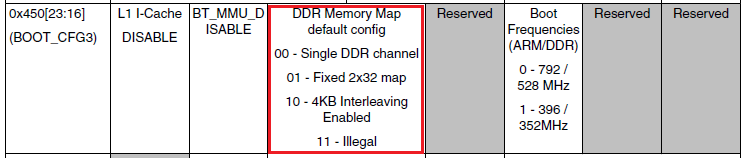

the OCOPT_CFG valuses are :

- OCOTP_CFG3 : 0x00620302

| bit | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

| values | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 |

then i think DDR Memmory Map default config bit[21:20] is 10(4kb interleaving Enabled).

but i got an answer from nxp team. it's Single DDR channel...

could you let me know why?

Best regards,

MyungJin Hwang

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Yuri.

Thanks for the reply...

then one more question.

How to find or know that BOOT_CFG[3] relates to OCOTP_CFG4?

is there some table info?

Have a great day,

MyungJin Hwang

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

To be oriented how register OCOTP_CFGx correspond to the fuses ,

please use column “Addr” in tables of Chapter 5 (Fusemap) and

column “Absolute address (hex)” in table in section 46.5 (OCOTP Memory

Map/Register Definition) of the i.MX6 D/Q RM.

For example, value of OTP Bank0 Word0 (Lock controls) (OCOTP_LOCK)

at 0x021B_C400 corresponds to Table 5-2. (Lock Fuses) with 0x400 offset.

Regards,

Yuri.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

The BOOT_CFG[3] relates to OTP Bank 0, word 5 : that is, bits 23-16 of

OCOTP_CFG4 should be used.

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------