- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

Current leakage on i.MX7D before power on sequence

The customer system is dual board design.

A board is Other brand CPU+OSC

B board is i.MX7D+XTAL

They shared A board's OSC clock channel to i.MX7D external clock input.

The configuration in kernel: SD1_DATA1 => CCM_EXT_CLK2

But the power time slot of A board is earlier than B board.

So SD1_DATA1 has clock input from A board OSC before i.MX7D start its power on sequence.

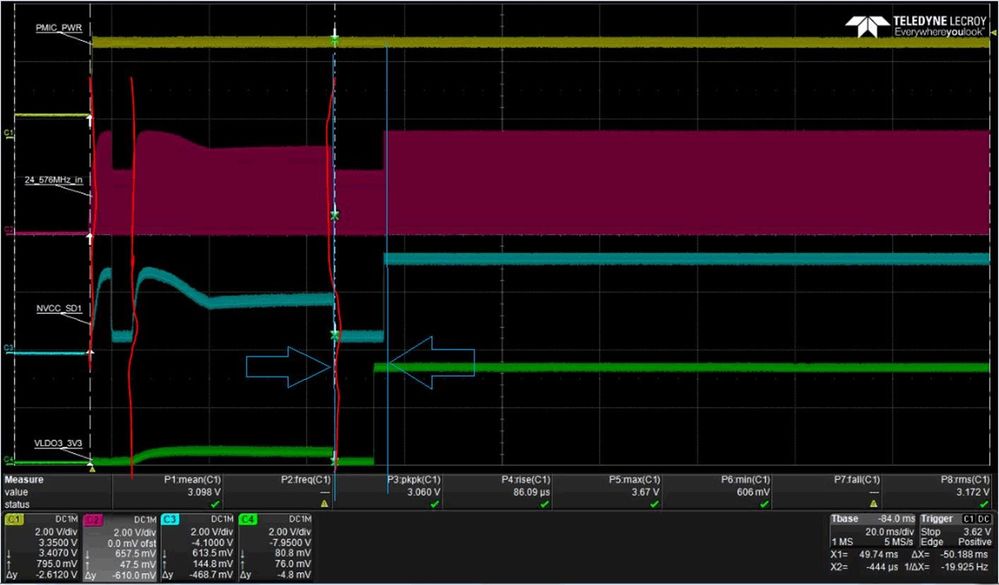

It causes current leakage into the other two pins(NVCC_SD1 & VLDO3_3V3).

Signal of SD1_DATA1 (Red)

Signal of NVCC_SD1(Blue)

Signal of VLDO3_3V3(Green)

The customer would like to know what is the side effect under this condition.

By the way,we get information from i.MX6 datasheet about current leakage of power on sequence.

But we can't catch any information like this on i.MX7D datasheet.

Is there any version difference on it?

Hello,

Section 4.1.11 (Power supplies usage) of the i.MX7 Datasheet (IMX7DCEC,

Rev. 5, 07/2017) states: "I/O pins should not be externally driven while the I/O

power supply for the pin (NVCC_xxx) is OFF. This can cause internal latch-up

and malfunctions due to reverse current flows."

Have a great day,

Yuri

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------