- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

Hi, NXP experts,

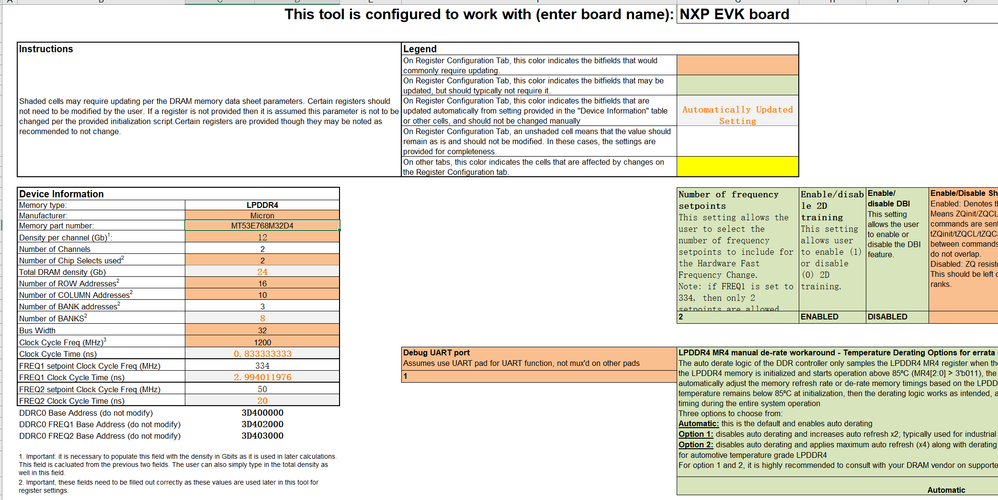

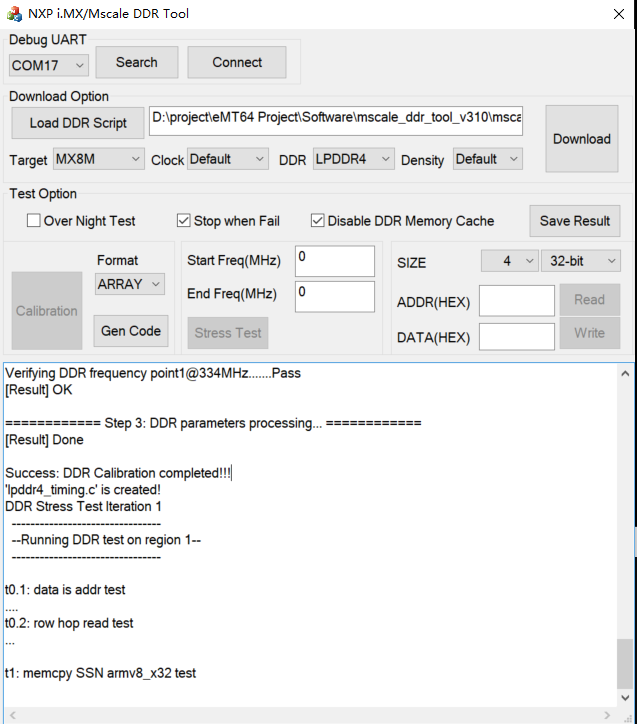

We run the i.MX8MQ EVK(LPDDR4 3GB) normally with LPDDR4 3200Mbps configuration, but when we try to run the i.MX8MQ EVK(LPDDR4 3GB) with LPDDR4 2400Mbps configuration , it seems that the access to memory encounter errors in the LPDDR4 timing. belows are our steps used by us:

1.fill the PRA sheet with 2400Mbps LPDDR4 config

2.use latest DDR stress tools to generate the code and config files

3.use the generated .c file to compile the SPL in which we add a function to do simple memory test.

4.when SPL boots up, it reports that all three training process PASS at frequency point 2400,667,2400.

5.the function which do simple memory test runs in internal SRAM space only.

6.after the initialization of DDR , the function which do simple memory test reports lots of errors which indicate the data dismatch between written and read data.

7.but no errors reported when we duplicate the same steps above with 3200Mbps config.

so , our question is , for NXP experts, :

1.Have you ever tried the same scenario(LPDDR4 2400Mbps config) on i.MX8MQ EVK(LPDDR4 3GB)?

2.could you please help us to check if there are any mistake in attached config files?

已解决! 转到解答。

Hi, all experts and user

after two weeks working , we finally find out the root cause of this issue. as below:

we use the 2017 version u-boot, in which the used ATF code use the fixed 3200Mbps speed to init the DDR interface, and if SPL(also included in u-boot code-package) use the non-3200Mbps speed as working speed of DDR interface , ATF will always change this non-3200Mbps working speed to the 3200Mbps speed, so some mismatches happened.

and then we change our code from 2017 version u-boot to 2020.04 version u-boot in which the ATF code will read the first rate(FSP[0]) in FSP array which is passed by SPL, placed in RAM space. ATF will use this read-backed speed as the initializing rate point. in one word, ATF in 2020.04 u-boot code-package will follow the config set by SPL code. so no mismatch is there!

FYI.

Hi, all experts and user

after two weeks working , we finally find out the root cause of this issue. as below:

we use the 2017 version u-boot, in which the used ATF code use the fixed 3200Mbps speed to init the DDR interface, and if SPL(also included in u-boot code-package) use the non-3200Mbps speed as working speed of DDR interface , ATF will always change this non-3200Mbps working speed to the 3200Mbps speed, so some mismatches happened.

and then we change our code from 2017 version u-boot to 2020.04 version u-boot in which the ATF code will read the first rate(FSP[0]) in FSP array which is passed by SPL, placed in RAM space. ATF will use this read-backed speed as the initializing rate point. in one word, ATF in 2020.04 u-boot code-package will follow the config set by SPL code. so no mismatch is there!

FYI.

in generated timing file of 2400Mbps , a obvious error is that tRTP is set to 6.66ns, but the LPDDR4 device datasheet says that tRTP should be MAX{7.5ns,8*tCK}.

in genertated timing file of 3200Mbps , tRTP is set to 7.5ns.

for NXP experts reference.

The 2400Mbps can work in theory. Here have you use the mkimage tool to generate the flash.bin file when finish compile u-boot with spl? And you said the 3200Mbps LPDDR4 works well, are you using the same method?

Hi,Rita wang,

for 3200Mbps config ,the pair of 'address/value' for register SDRAM Timing Register 1 (DRAMTMG1) is { 0x3d400104, 0x506a6 }, which will result a final value of tRTP=7.5ns, and this tRTP=7.5ns is valid setting for Micron LPDDR4 device.

FYI. and

wait for your feedback.

thanks.

Hi,b45499,

thanks for your attention to this .

We do use the mkimage tool(same method) to generate the flash.bin for both 2400Mbps(1200MHz clock) config and 3200Mbps(1600MHz clock) config.

and more info below:

there are (address, value) pair in config file lpddr4_timing.c, one of these pairs is { 0x3d400104, 0x504a6 }, which indicates the register(SDRAM Timing Register 1 (DRAMTMG1)) at addresss 0x3d400104 should be set as 0x504a6. and in this register , the field rd2pre is bit[13:8](0x4 or 0'b0100) , and it is explained as

tRTP: Minimum time from read to precharge of same bank.

- DDR2: tAL + BL/2 + max(tRTP, 2) - 2

- DDR3: tAL + max (tRTP, 4)

- DDR4: Max of following two equations: tAL + max (tRTP, 4) or, RL + BL/2 -tRP (*).

- mDDR: BL/2

- LPDDR2: Depends on if it's LPDDR2-S2 or LPDDR2-S4: LPDDR2-S2: BL/2 +tRTP - 1. LPDDR2-S4: BL/2 + max(tRTP,2) - 2.

- LPDDR3: BL/2 + max(tRTP,4) - 4

- LPDDR4: BL/2 + max(tRTP,8) - 8

(*) When both DDR4 SDRAM and ST-MRAM are used simultaneously, use SDRAM's tRP value for calculation.

When the controller is operating in 1:2 mode, 1T mode, divide the above value by 2. No rounding up.

When the controller is operating in 1:2 mode, 2T mode or LPDDR4 mode, divide the above value by 2 and round it up to the next integer value.

Unit: Clocks.

so the tRTP timing value(in hardware Memory Controller,BL=16 for LPDDR4 usage) should be BL/2 + max(tRTP,8) - 8 = 8*tCK=8*(1/1200M)=6.66ns.

but in datasheet of Micron LPDDR4 device , the tRTP should be MAX{7.5ns,8*tCK} which is in attached picture.

and could you please help confirm if 2400Mbps config could really work well ?

thanks.