- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

-

- Home

- :

- i.MX Forums

- :

- i.MX Processors

- :

- Board Bringup - No JTAG Response - What are the most basic requirements for JTAG response?

Board Bringup - No JTAG Response - What are the most basic requirements for JTAG response?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Using a custom board very similar to the Sabre Lite using an IMX6 quad core, the board is not booting. Taking a step back, JTAG does not have a response (see output below) and can not ID the chip. Power supplies were confirmed to be sequenced properly, are at the proper DC level, and are clean DC for both input supplies and generated supplies VDDARM23_CAP, VDDARM_CAP, and VDDPU_CAP. Reset circuit signals are also correct, toggling ON 600ms after the supplies are stable. If the power supplies are ok and the jtag connections are ok, is there anything else that could prevent JTAG from working?

I've confirmed also that the jtag tool and cabling works ok by using it on a Sabre Lite board.

Thank you for any suggestions you can offer.

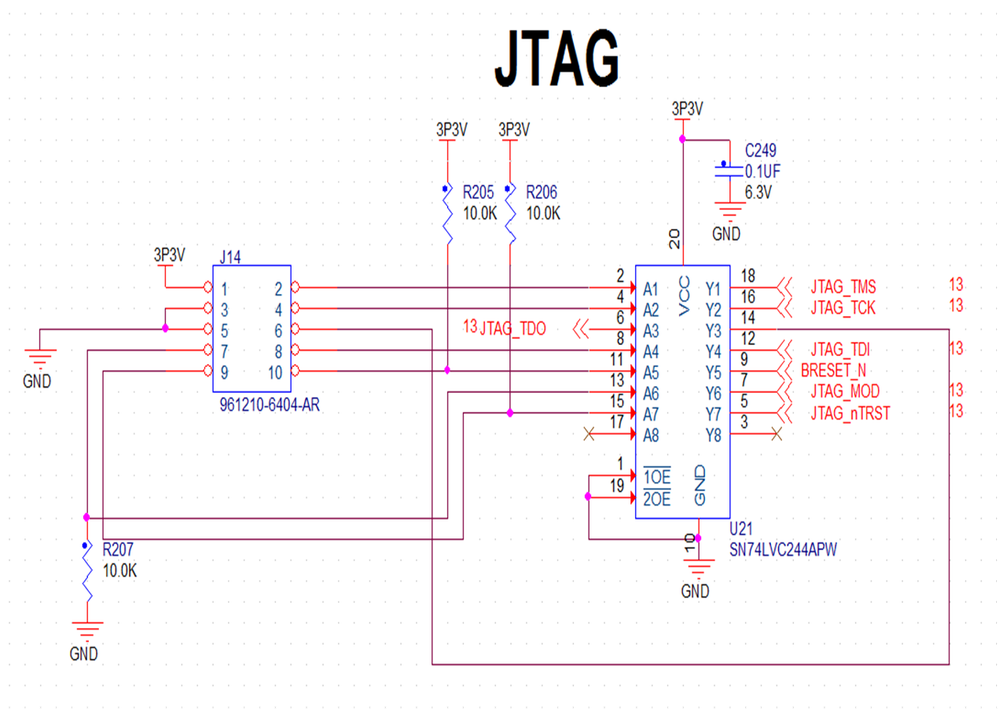

JTAG circuit:

----------------------------------

JTAG Output:

----------------------------------

SEGGER J-Link Commander V4.98e ('?' for help)

Compiled May 5 2015 11:01:31

DLL version V4.98e, compiled May 5 2015 11:00:52

Firmware: J-Link ARM / Flasher ARM V4 compiled Mar 31 2015 22:22:18

Hardware: V4.00

S/N: 164102666

Feature(s): JFlash, GDB

IP-Addr.: 255.255.255.255 (DHCP)

VTarget = 3.282V

Info: Could not measure total IR len. TDO is constant high.

Info: Could not measure total IR len. TDO is constant high.

No devices found on JTAG chain. Trying to find device on SWD.

No device found on SWD.

Failed to identify target. Trying again with slow (4 kHz) speed.

Info: Could not measure total IR len. TDO is constant high.

Info: Could not measure total IR len. TDO is constant high.

No devices found on JTAG chain. Trying to find device on SWD.

No device found on SWD.

No device found at all. Selecting JTAG as default target interface.

J-Link>

--------------------------------------

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jeff

one can check that JTAG_MODE=0, NVCC_JTAG is applied.

For bsld operation one needs to have PCIE_VP, PCIE_VPH, PCIE_VPTX

powered (from Table 2-21. Recommended connections for unused analog interfaces IMX6DQ6SDLHDG)

One can also check sect.2.6 JTAG signal termination, Chapter 7 Configuring JTAG Tools,http://cache.freescale.com/files/32bit/doc/user_guide/IMX6DQ6SDLHDG.pdf?fasp=1&WT_TYPE=Users%20Guide...

check that 24MHz and 32.768KHz clocks are running.

Blowing fuse SJC_DISABLE disabes jtag (from Table 5-10. Fusemap Descriptions IMX6DQRM)

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jeff

one can check that JTAG_MODE=0, NVCC_JTAG is applied.

For bsld operation one needs to have PCIE_VP, PCIE_VPH, PCIE_VPTX

powered (from Table 2-21. Recommended connections for unused analog interfaces IMX6DQ6SDLHDG)

One can also check sect.2.6 JTAG signal termination, Chapter 7 Configuring JTAG Tools,http://cache.freescale.com/files/32bit/doc/user_guide/IMX6DQ6SDLHDG.pdf?fasp=1&WT_TYPE=Users%20Guide...

check that 24MHz and 32.768KHz clocks are running.

Blowing fuse SJC_DISABLE disabes jtag (from Table 5-10. Fusemap Descriptions IMX6DQRM)

Best regards

igor

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It was the clock source! I changed it to a 16MHz and I am now able to JTAG ID the chip! It is possible the 24MHz crystal was damaged. I'll experiment further by changing to a new 24MHz source and step through the boot process. It is great to see it finally has a pulse. Thanks!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for your thoughts. Here's what I checked:

JTAG_MODE is 0,

NVCC_JTAG is 3.3V,

PCIE_VP=VDDSOC_CAP(1.112V),

PCIE_VPH=2.5V

VCIE_VPTX=VDDSOC_CAP (filtered 1.112V)

JTAG terminations are outputs of a buffer IC that has pull-up\pull-downs as inputs, except TMS and TCK floating input to buffer, and TDO is a floating input to the buffer (no pullup\pulldown) per docs, so it all seems to comply.

The clock sources do not seem to be running. I will try to get them running (perhaps it is a load capacitance problem), but I assumed the chip could run via jtag without the clock sources - do you know?

The IMX6 IC is new from a reputable distributor (Digikey), so the fuses should be default. I can't confirm without JTAG working.

Thanks for your help. If you know about whether clock sources are needed for JTAG, that would help further. Also open to other ideas.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jeff

I noticed one more thing. Can you put pull-ups on TMS

and TCK pins. (pin #2 and #4). Also I see that your RESET_N

is pulled high (pin 10). Can you remove that pull-up and

scope this as well.

Hope this helps.

Sinan Akman

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I scoped TDO before the buffer and confirmed as the JTAG output is reporting - it stays constant high. Next, I added pull-ups to TMS and TCK, removed the reset pull-up and confirmed the same JTAG response. I see that RESET_N toggles, as controlled by the JTAG software\hardware, but TDO stays high.

Thanks for your help, but it is still unable to jtag ID the chip. If you have any other suggestions or ideas, I'm open to trying them\checking.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jeff

If power supplies are correct and despite TMS. TCK

activity if you see no signal on TDO, what comes to

my mind is that perhaps your SoC has enabled secure

boot with no JTAG. Are any fuses blown on this SoC ?

Sinan Akamn

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sinan Akman,

I have come across your post and looks like you have good understanding of BDI3000 on imx6 platform.Do you have some steps to load u-boot to SRAM on sabrelite base custom board using BDI3000 debugger.

Regards

Sanjeev Sharma

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sanjeev

What you need is essentially a config file for BDI3000 that

initializes the SRAM and a version of u-boot that does not

do those initialization. You can then RESET HALT via

your BDI3000 then load the u-boot image to memory and

run it from there.

I suggest that you start a new thread for your question as it

is now different than the original question for this thread.

We can then all follow up on the new thread. Please note

that I am traveling during the next few weeks so my response

might be delayed sometimes.

Regards

Sinan Akman

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Well, I have (3) prototypes, all built with new chips from Digikey. I don't have any way of knowing about the fuse status, but it should be running defaults. Thanks for your ideas.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jeff

Can you scope JTAG_TDO before it goes into

the buffer ?

Regards

Sinan Akman