- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- About Non-Gated Clock Mode issue of the Parallel CSI module on the i.MX 6ULL series MPU.

About Non-Gated Clock Mode issue of the Parallel CSI module on the i.MX 6ULL series MPU.

オプション

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

解決済み

12-01-2020

08:13 PM

1,049件の閲覧回数

vikenzhou

Contributor I

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, I am have a question about the Parallel CSI module, hope here can get answer, thank you!

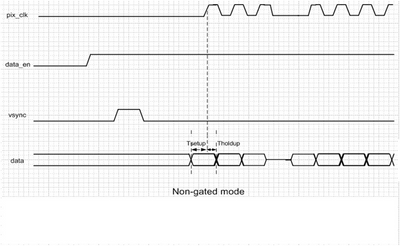

When MPU is running in Non-Gated Clock Mode, because the HSYNC signal will be ignored,

How know a line the number of pixels, it is possible using the clock edge to latched data; if so, in this Parallel_CSI_TX side, the pixel data of a line can many discontinuous clock cycles to send out ?

Please see below the figure, thank you!

How know a line the number of pixels, it is possible using the clock edge to latched data; if so, in this Parallel_CSI_TX side, the pixel data of a line can many discontinuous clock cycles to send out ?

Please see below the figure, thank you!

解決済! 解決策の投稿を見る。

1 解決策

12-01-2020

11:44 PM

1,043件の閲覧回数

NXP TechSupport

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

4 返答(返信)

12-02-2020

12:58 AM

1,033件の閲覧回数

vikenzhou

Contributor I

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thans for your great support, the following questions please help guide again, thank you!

1, I have to see the pictures of you reply which is included a Data_EN signal, the signal in the Parallel_CSI_RX is necessary? The figure 19 on page758 of document (IMX6ULLRM.pdf), Here is no use this Data_EN signal.

2, When sending a line of pixels, is the need for a continuous clock to send a line, or send a line of pixels can be discontinuous .

12-01-2020

11:44 PM

1,044件の閲覧回数

NXP TechSupport

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

for non-gated mode, pls see the pic as below:

12-02-2020

06:41 PM

1,021件の閲覧回数

vikenzhou

Contributor I

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Why in rev.1 Reference Manual there is no Data_EN .

12-02-2020

01:00 AM

1,029件の閲覧回数

vikenzhou

Contributor I

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告