- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- i.MX フォーラム

- :

- i.MXプロセッサ

- :

- About ASI master clock of MX6UL

About ASI master clock of MX6UL

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear all,

I want to use SAI of i.MX6UL.

I refer to Chapter 43 of RM.

http://cache.freescale.com/files/32bit/doc/ref_manual/IMX6ULRM.pdf

- Chapter 43 Synchronous Audio Interface (SAI)

I have some questions.

<Q1>

I understand the Master Clock of SAI is generated by SAIx_CLK_ROOT.

Is SAIx_CLK_ROOT connected directly with Master Clock of SAIx?

<Q2>

In MCLK Select field of I2Sx_TCR2 register, audio Master Clock option can be chosen.

However, I cannot find the explanation about these options.

Would you tell me the point where this is explained?

<Q3>

In MCLK Select of the I2Sx_RCR2 register, would you tell me the concrete clock name of "00:Bus Clock selected"?

May I have advice?

Best Regards,

Yuuki

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Yuuki

If you refer to section 18.3 “CCM Clock Tree” of the same Reference Manual you will see the origins and destinations of each clock signal, including SAI1_CLK_ROOT, SAI2_CLK_ROOT and SAI3_CLK_ROOT.

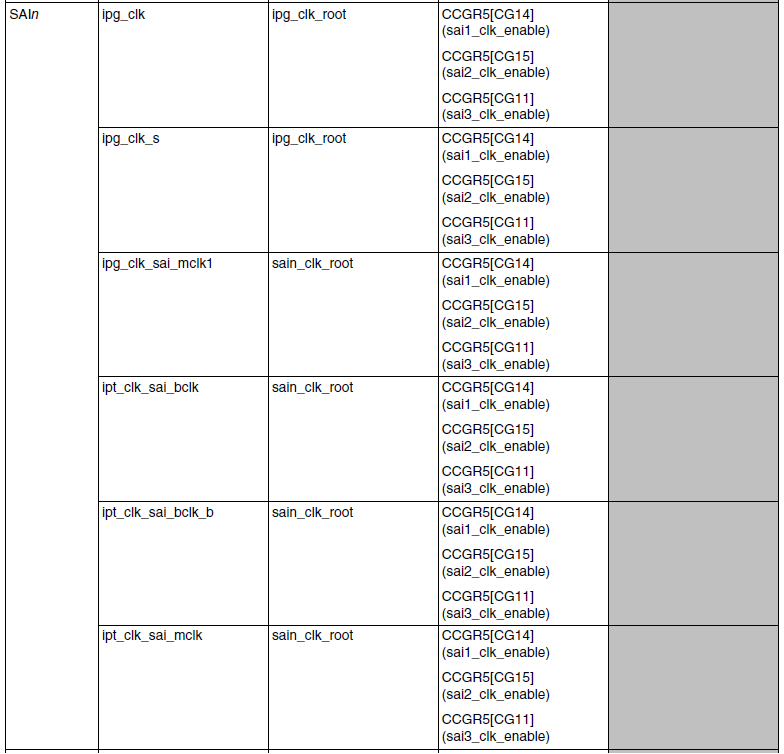

Then, on section 18.4, the Table 18-3 shows the CCM output clocks' system-level connectivity. The following picture shows the SAI’s clocks:

Hope this will be useful for you.

Best regards!

/Carlos

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi:

Why the SAI1_MCLK Can't output to the Pin.

my configuration:

Use Pad : CSI_DATA01, Mode(ALT6), PAD_CTL (Pull up with 47kohm, SPEED_3_max_200MHz, Fast_Slew_rate)

The other signal of the SAI (include BCLK、SYNC、DATA) are all output correctly.

Help me out,Tks

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

HI

are you solved this problem?

i have same issue. if you solved,please share it with everyone!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Yuuki

If you refer to section 18.3 “CCM Clock Tree” of the same Reference Manual you will see the origins and destinations of each clock signal, including SAI1_CLK_ROOT, SAI2_CLK_ROOT and SAI3_CLK_ROOT.

Then, on section 18.4, the Table 18-3 shows the CCM output clocks' system-level connectivity. The following picture shows the SAI’s clocks:

Hope this will be useful for you.

Best regards!

/Carlos

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

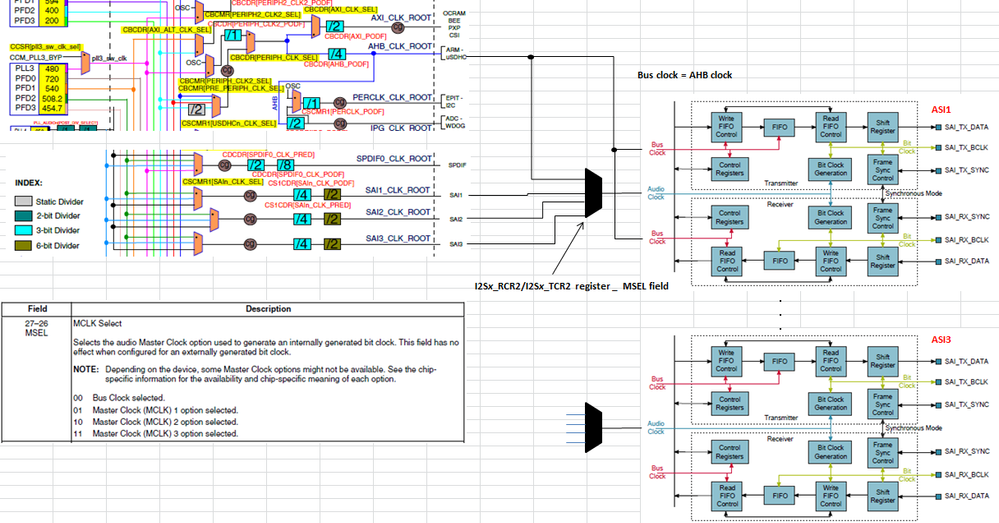

Dear CarlosCasillas-san,

Thank you for your support.

I understood that those clock were connected like the following figure.

- MCLK of each ASI is supplied from ASIx_CLK_ROOT.

- Clock source (SAIx_CLK_ROOT) is chosen by MSEL field.

- The Bus clock means AHB CLK(AHB_CLK_ROOT).

Is my understanding right?

Best Regards,

Yuuki

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Yuuki,

Yes, you are right!

Best regards!

/Carlos

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------