- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- Vybrid Processors

- :

- Re: SAI bus clock selection

SAI bus clock selection

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I tried to verify which clock exactly is slected by the SAI bus clock selection (TCR2[MSEL]=0).

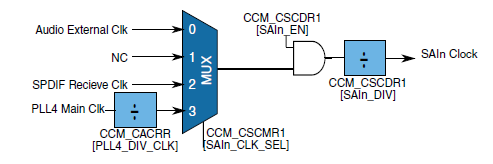

Let's start from the obvious: When I set TCR2[MSEL] = 01, I get the clock defined CCM_CSCMR1[SAIn_CLK_SEL], more over the whole logic including the gate CCM_CSCDR1[SAIn_EN] and the divider CCM_CSCDR1[SAIn_DIV] works as documented in Chapter 9.10.12 SAI clocking.

However, when switching to TCR2[MSEL] = 00, unexpectetly the output clock does not change. Also, when I use the gate from above (CCM_CSCDR1[SAIn_EN]) my bit clock gets disabled too, hence it looks like the two MSEL are actually the same SAIn clocks, as configured in CSCMR1 and friends. Is this really the case or am I missing something? IMHO, the documentation is somewhat unclear if Bus Clock actually really selects the SAIn clock too...

--

Stefan

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are marking this post as solved, due to the either low activity or any reply marked as correct.

If you have additional questions, please create a new post and reference to this closed post.

NXP Community!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are marking this post as solved, due to the either low activity or any reply marked as correct.

If you have additional questions, please create a new post and reference to this closed post.

NXP Community!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Stefan,

No other setting just TCR2[MSEL] and if TCR2[MSEL]=1 then CCM_CSCMR1 is used:

Please check if TE is enabled. TCR2 register must not be altered when TCSR[TE] is set.

You can also check clocks using 10.2.14 CCM Clock Output Source Register (CCM_CCOSR)

/Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jiri,

Sorry, maybe I was a bit unclear, but this does not really answer my question. I do get an output clock. my concern is the possible selection using TCR2[MSEL]

My question is: Which clock is used if TCR2[MSEL] is b00. According to the reference manual, chapter 3.11.1.2.3 "SAI transmitter and receiver options for MCLK selection", table Table 3-30, b00 is "Bus Clock". However, it looks like it is the same as when using b01, hence not bus clock, but clock selected by SAIn_CLK_SEL...

--

Stefan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Stefan,

if TCR2[MSEL] == 0 then it is bus clock (IPS bus clock), which is 133-166MHz/2 if IPG_CLK_DIV=2

if TCR2[MSEL] == 1 then is used clock defined in CCM_CSCMR1 so it can be External clock, SPDIF clk or PLL4 Main clk.

please check if TE is enabled - TCR2 register must not be altered when TCSR[TE] is set.

/Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jiri,

I explicitly write a 0x0 to TCSR, then change TCSR[MSEL] to b00, and enable TE again, however, I still get 73.735MHz. I also tried from the reset state, by setting TCSR[MSEL] to 0 before ever enabling the transmitter.

The measured clock with TCSR[MSEL] b00 is 73.725MHz, which seems to be the SAI clock. PLL Audio is at it's default value of 1176MHz divided by the 8 using CCM_CACRR[PLL4_CLK_DIV] and another 2 by the minimal divider of SAI. I would expect 83.3MHz/2 as output on my module (500MHz system clock, 166MHz bus clock => 83.3MHz IPG clock).

--

Stefan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Stefan,

I can try it later, but if you select TCR2[MSEL] == 0 and IPG_CLK_DIV=2 and platform clock is 150MHz then IPB bus clock is 75 MHz. - this is correct.

What is your configuration in TCR2[MSEL] == 1 ?

/Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jiri,

The platform clock is 166MHz, hence I would epxect ~41.6MHz as output clock (/2 due to IPG, /2 in SAI).

When using TCR2[MSEL] = b01, we use PLL4 main clock at 1176MHz with CCM_CACRR[PLL4_CLK_DIV] divider of 8.

--

Stefan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Stefan,

I will try it. Will create test project with clockout and measure it in WW8. If you have code which you can share and which does not work for you - upload it please.

/Jiri

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What we use is basically the driver in mainline Linux kernel I pointed to above in the answer to Alejandro. I just tried to use the bus clock instead of the SAI clock.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

alejandrolozano can you continue with the follow up?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sure, I just tested with MQX and just like Stefan mentioned the MCLK does not change modifyng the MSEL bit.

jiri-b36968 I wonder if you have some baremetal project Stefan and I can use to test and narrow down the possible issue.

Best Regards,

Alejandro

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alejandro,

Sorry, I do not have a bare metal project. This appeared while working on a Linux SAI driver. I also do not have DS-5 development environment setup up to create a bare metal project quickly.

To me, it really looks like a hardware issue...

--

Stefan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Stefan,

I asked jiri-b36968 if there is some validation code we can use as reference. That will help to identify it is a hardware issue. If you do not have DS-5 I can test it for you.

/Alejandro

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

jiri-b36968 any comment?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

falstaff can you share the status here?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry, I was not aware that actions from my side are currently required. I do not have DS-5 installed... alejandrolozano can you test the validation code?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Stefan,

I have double checked the previous code of MQX and using as reference the code Jiri sent I noticed that I was not measuring correctly.

The setting to choose a different clock works. I was using a different SAI instance and therefore I never noticed the change.

You can measure that change too with this code in the PTB11 pad.

I my case I try to see an externa audio clock, but there is not exist such source clock and therefore I do not see a clock output. This all means that the clock change works and it is not a hw problem.

| /*CKO outputs via PTB11 PTB10 */ | |

| IOMUXC_RGPIO(32) = 0x00603062; | |

| IOMUXC_RGPIO(33) = 0x00603062; |

| CCM_CCOSR = 0x040F07C7 |

Which code you have changed in Linux BSP? I will check it out

Best Regards,

Alejandro

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alejandro,

Sorry it took me a while to respond. I did not try to use CKO1 to access SAI0 clock, quite possible that this is working. The problem does not seem to be the CCM_CSCMR1[SAIn_CLK_SEL] selection, but within the SAI IP itself.

The clock selection I'm trying to switch is SAIx_TCR2[MSEL]....

When using TCR2[MSEL] = 01, I expect the clock defined in CCM_CSCMR1 so it can be External clock, SPDIF clk or PLL4 Main clk. => This works fine!

When using TCR2[MSEL] = 00, I expect bus clock (IPS bus clock) as SAI input clock => This does not work. I get the same clock as when using 01 (like above)

So, what I'm saying is, that TCR2[MSEL] = 00 does not allow to select the IPS bus clock as documented...

--

Stefan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Stefan and Karina,

In fact I was going to test the validation code Jiri sent, but last week I was swamped.

I will start testing today. I will let you know my findings Stefan.

Best Regards,

Alejandro