- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

Hi,

We connected a analog camera to an external video-decoder (adv7180) which is connected to the viu using the 8bit itu656-interface (Vybrid VF512R3CMK4).

When we start the video-decoder it sends out the serial protocol, and we can see correctly the protocol (SAV/EAV starting with FF 00 00 XX, where XX has different state for field/vsync/hsync, ...)

The VIU detects field-irqs, but we don't get any vsync-irq.

Although we don't get any error-irqs, so it seams that the received protocol is correct (see ecc-errors in scr-register of viu), but the internal decoder from the viu-module doesn't generate a vsync-irq.

Has anybody use the viu using the 8bit itu656-mode ??

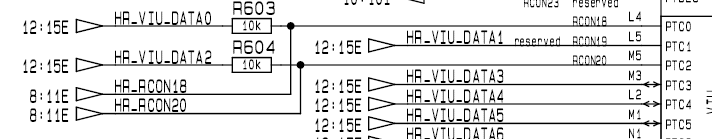

Here's the pining

PTC2 -> VIU_DATA2

PTC3 -> VIU_DATA3

PTC4 -> VIU_DATA4

PTC5 -> VIU_DATA5

PTC6 -> VIU_DATA6

PTC7 -> VIU_DATA7

PTC8 -> VIU_DATA8

PTC9 -> VIU_DATA9

PTB16 -> VIU_DATA10

PTA7 -> VIU_PIX_CLK

Another question is : How does the viu differ between 8bit and 10bit itu656-mode ?

Regards

Sebastian

已解决! 转到解答。

Hi Sebastian,

we have checked all lines. If there are correctly connected to Vybrid: there is an issue on the board:

between External ADC and VIU data 2 is 10k resistor:

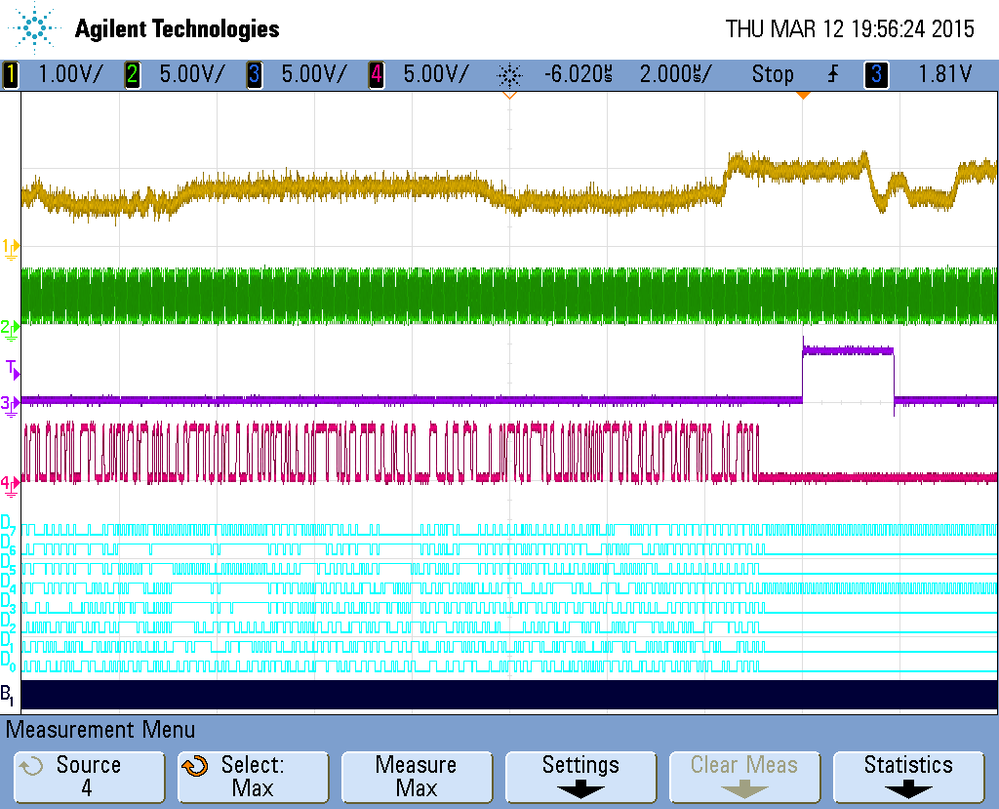

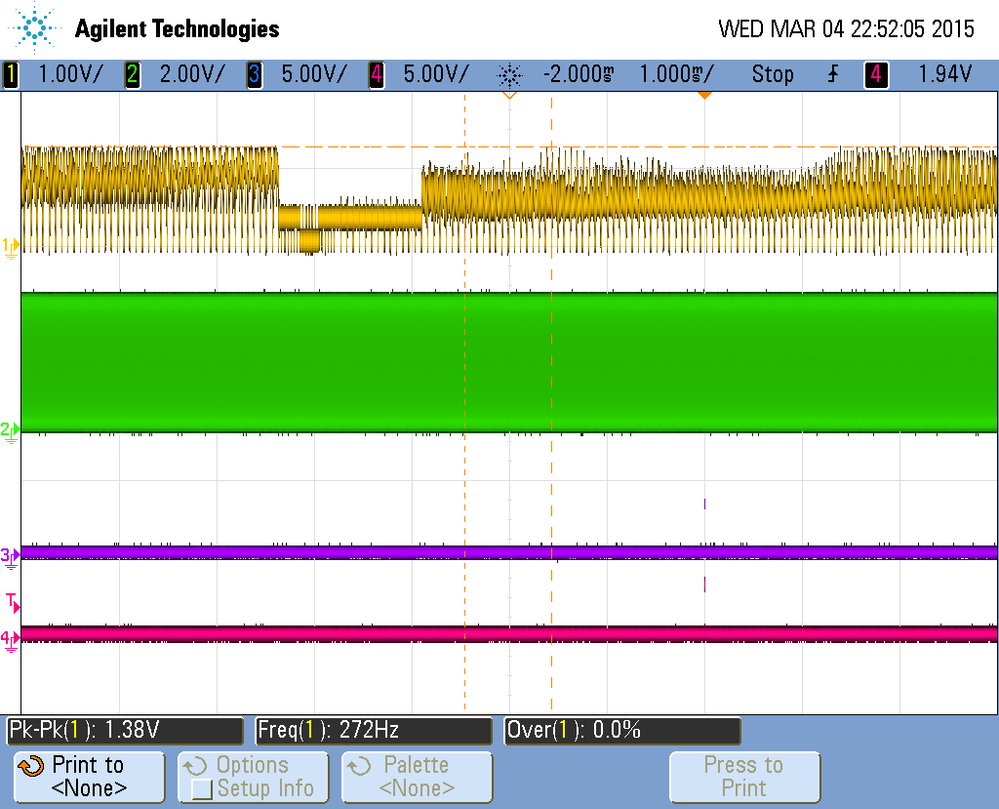

Measurement1:

Yellow is Analog

Red line is D2 (HR_VIU_DATA2) - before resitor

Green is clk

Light blue are D9 to D2

Red line is D2 (PTC2) - after resistor

So signal on D2 is not correctly connected.

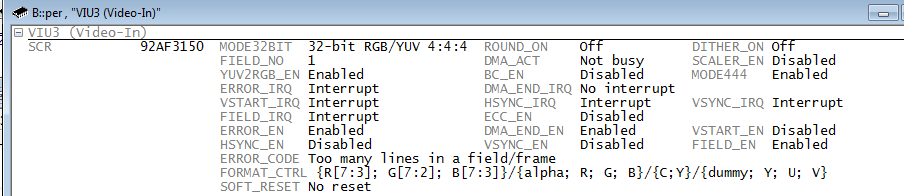

Current state on terminal:

----------------------------------------------------------------------

Decoder Status (IN_LOCK): yes

Decoder Status (LOST_LOCK): no

Detected Video Standard: NTSC M/J

Correct line length detected: yes

Correct field length detected: yes

Interlaced video detected: yes

----------------------------------------------------------------------

Capture start !!!

VIU3 state is BUSY!

VIU3 state is BUSY!

VIU3 state is BUSY!

VIU3 state is BUSY!

VIU3 state is BUSY!

VIU3 state is BUSY!

VIU3 state is BUSY!

VIU3 state is BUSY!

VIU3 state is BUSY!

VIU3 state is BUSY!

Error stopping the VIU3 device, returned: 0xffffffff

VIU3 state is ERROR, error code is 47!

Device reset !!!

VIU3 state is READY!

Capture start !!!

VIU3 state is BUSY!

VIU3 state is BUSY!

...

...

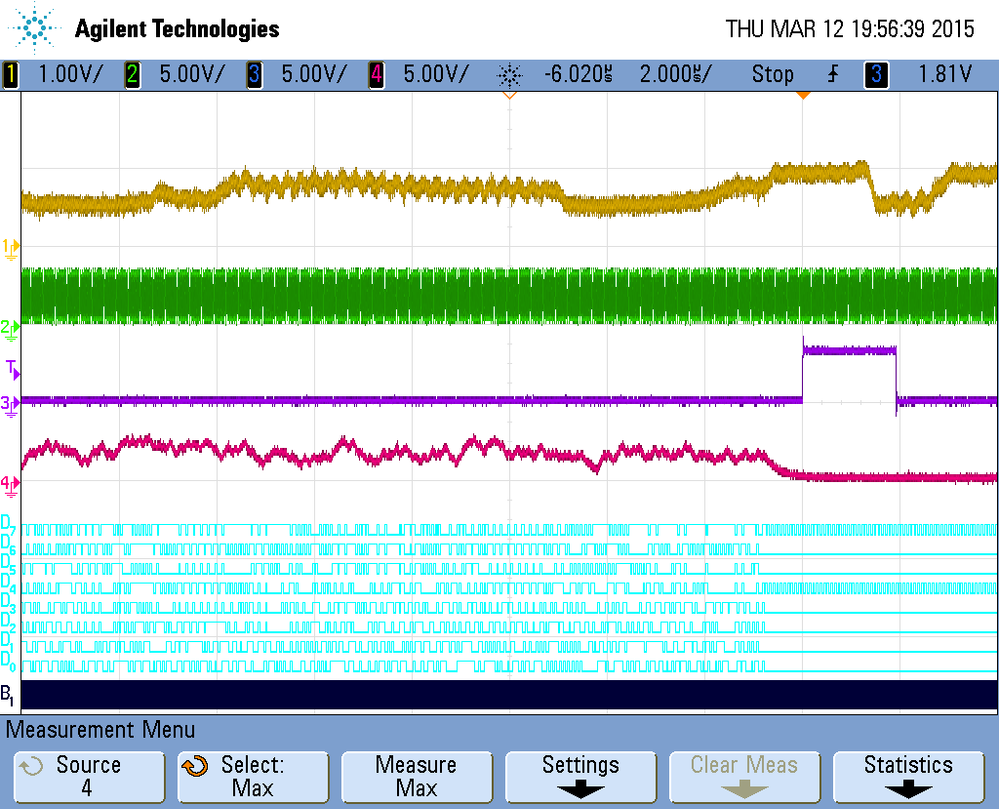

We removed R604 and placed 0R - situation has changed significantly. signal on PTC2 is correct.

After resistor removal on terminal:

----------------------------------------------------------------------

Decoder Status (IN_LOCK): yes

Decoder Status (LOST_LOCK): no

Detected Video Standard: NTSC M/J

Correct line length detected: yes

Correct field length detected: yes

Interlaced video detected: yes

----------------------------------------------------------------------

Capture start !!!

VIU3 state is ERROR, error code is 7!

Device reset !!!

VIU3 state is READY!

Capture start !!!

VIU3 state is ERROR, error code is 5!

Device reset !!!

VIU3 state is READY!

Capture start !!!

VIU3 state is ERROR, error code is 5!

Device reset !!!

...

...

Error 7 is not enough lines

Error 5 is too many lines.

All interrupts are generated .

So now you have to change setting of the interface.

/Jiri

Hi,

I think, that you connect a few pins. If you use VIU, you need connect by VSYNC and HSYNC. Then you can use IRQ from these.

And have you got true setting of VIU? Can you send your register setting?

Regards,

Vilem

Hi,

In RM (version 7) there is a table in chapter 57.3 "Video Input Signal Mapping", where HSYNC, VSYNC, DE and FID is not connected for ITU656.

In chapter 57.5.3 "Decoder" is explained that HSYNC, VSYNC and FID are extracted from the ITU656-protocol. That's why we didn't connect these signals.

Do we have to connect them ?

I have attached an register-dump in a situation where we initialized the external decoder (which sends the 656-protocol).

The field-number changes periodically, so it seems that the decoder can successfully extract it, but we don't get any VSYNC-irq.

Regards,

Sebastian

Hi,

It's true. I'm sorry. It is my fault. For connections:

I think that you don't need VIU_DATA10 (chapter 57.3 in RM). You need only from VIU_DATA2 to VIU_DATA9. But this connection isn't correct. VIU_DATA10 must to be connect to pin PTB19 (ALT6 for mux).

And VIU_DATA9 is not correct connection. In chapter 5.1 in RM is table for PIN MUX and for VIU_DATA9 you need connect to PTB18 (ALT6 for MUX).

Another question is : How does the viu differ between 8bit and 10bit itu656-mode ?

To avoid confusion between 8-bit and 10-bit representations, the eight most significant bits are considered to be an

integer part while the two additional bits, if present, are considered to be fractional parts

For example, the bit pattern 10010001 would be expressed as 145d or 91h, whereas the pattern 1001000101 is expressed

as 145.25d or 91.4h.

From this documet: http://www-inst.eecs.berkeley.edu/~cs150/Documents/ITU656.PDF (page 2 - NOTE 1)

Can you try now?

And why do you use external video-decoder. You can use analog input in Vybrid.

Is ok?

Vilem

Hi Vilem,

I have reviewed our hardware. My connection-table above is wrong. Our hardware is connected as you described:

PTC2 -> VIU_DATA2

PTC3 -> VIU_DATA3

PTC4 -> VIU_DATA4

PTC5 -> VIU_DATA5

PTC6 -> VIU_DATA6

PTC7 -> VIU_DATA7

PTC8 -> VIU_DATA8

PTB18 -> VIU_DATA9

PTA7 -> VIU_PIX_CLK

So this is not the reason why viu doesn't work.

Does anybody use successfully the viu in itu656-mode ?

Regards

Sebastian

Hi Sebastian,

I'm afraid that HSYNC_IRQ and VSYNC_IRQ interrupts as raised only when VSYNC and HSYNC signals are used (need to be confirmed with designers). ITU is using just fields (FIELD_IRQ) and VSYNC and VSYNC are decoded.

Please try to use DMA_END_IRQ (VSTART_IRQ). Do you see them raising?

/Jiri

Hi Jiri,

as explained above, I only get the FIELD_IRQ. When I start the DMA-Transfer I never get an DMA_END_IRQ and DMA_ACT stays busy.

Is it even possible to use the ITU-mode without external HSYNC/VSYNC-signals connected ?

Regards

Sebastian

Hi Sebastian,

HSYNC/VSYNC are decoded from field in the case of ITU. No external HSYNC/VSYNC signal. Each received field triggers FIELD_INT. I would expect that is should generate also others interrupts after decoding. Since you say that it is not generated I'm going to ask designers and validation team. Stand-by.

/Jiri

Hi Sebastian,

designers claim that V/H sync should be generated in ITU mode.

Could you check if interval between FIELD_IRQ equals to one field and it is regular? Do you see correct field received - with V and H sync information?

/Jiri

Hi Jiri,

Sorry for my late answer but I was ill the last 2 weeks.

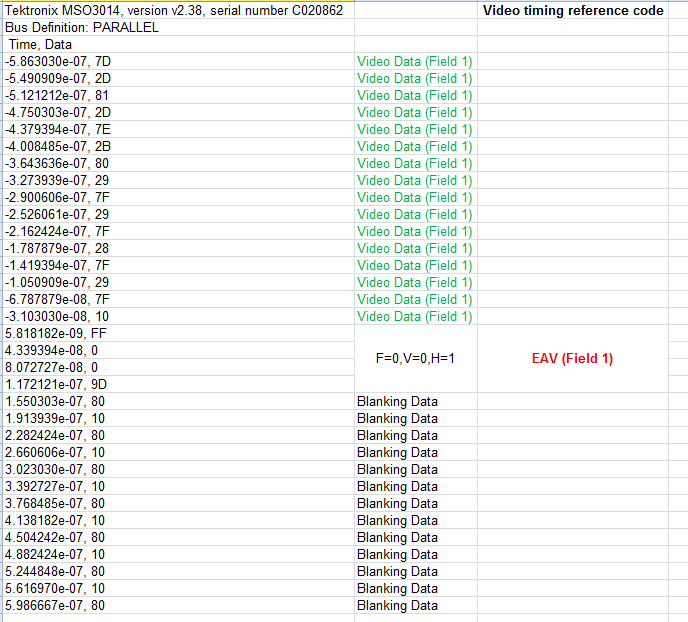

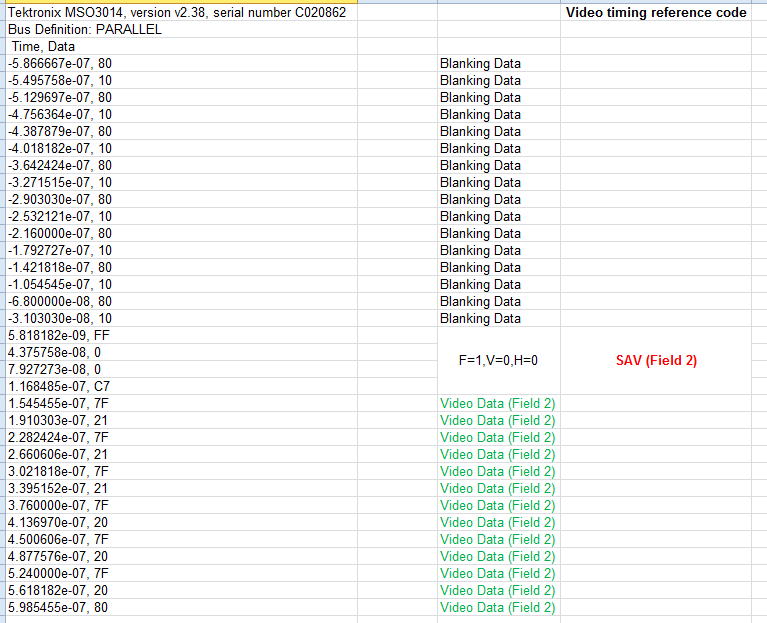

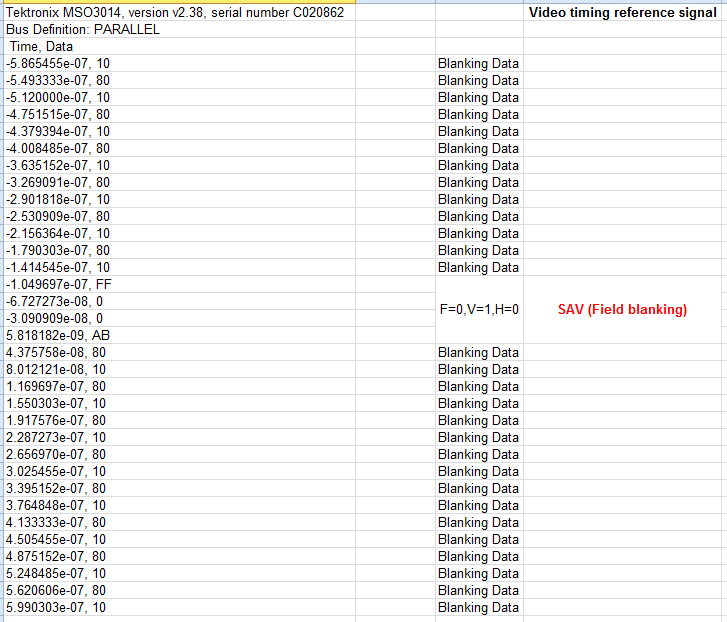

I have attached some example records where you can see the relevant ITU data-stream (SAV/EAV starting 0xFF, 0x00, 0x00).

Regards

Sebastian

Hi Sebastian,

Thank you for data. Those data are on input of VIU interface. Do not understand their timing from those pictures, sorry. Could you correlate those data (frames) with FIELD_IRQ generation, please? In which cases it is generated and at what intervals (add toggle GPIO for example)? Or at least what is interval of FIELD_IRQ generated on your board and is it regular?

/Jiri

Hi Sebastian,

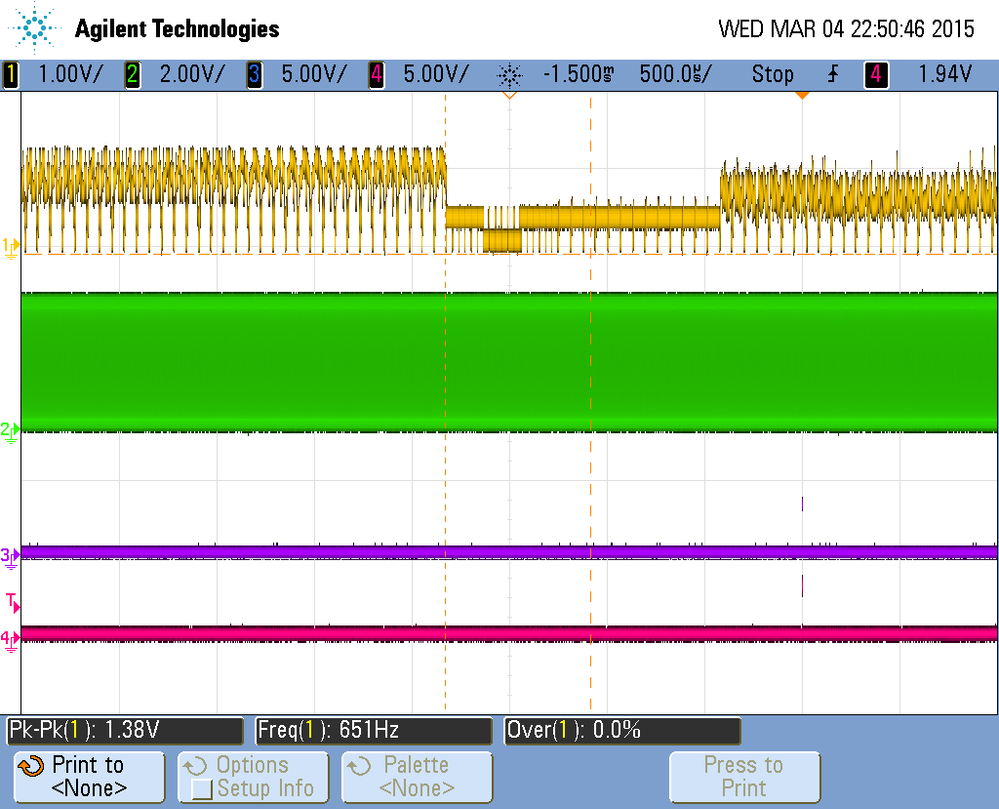

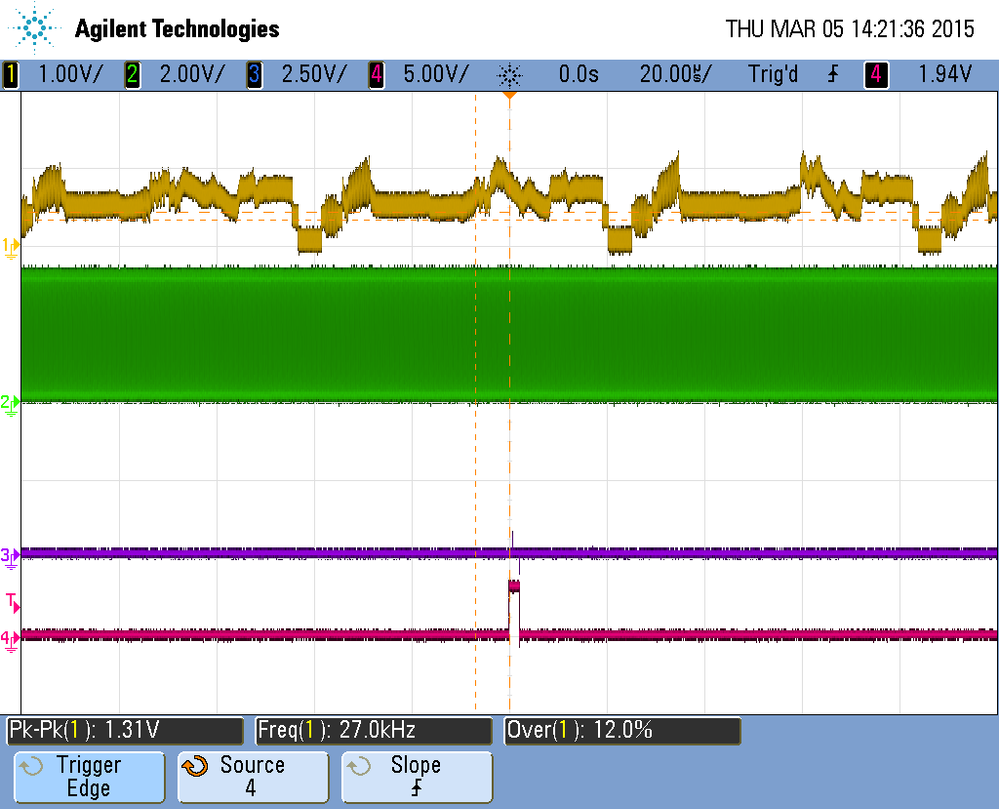

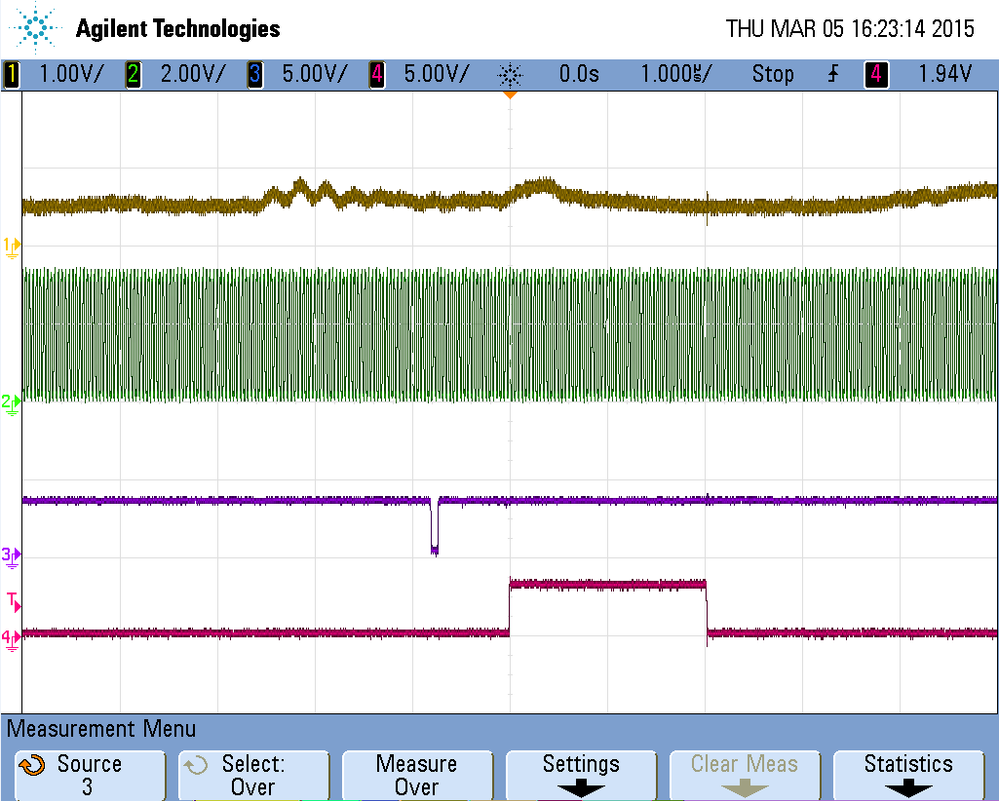

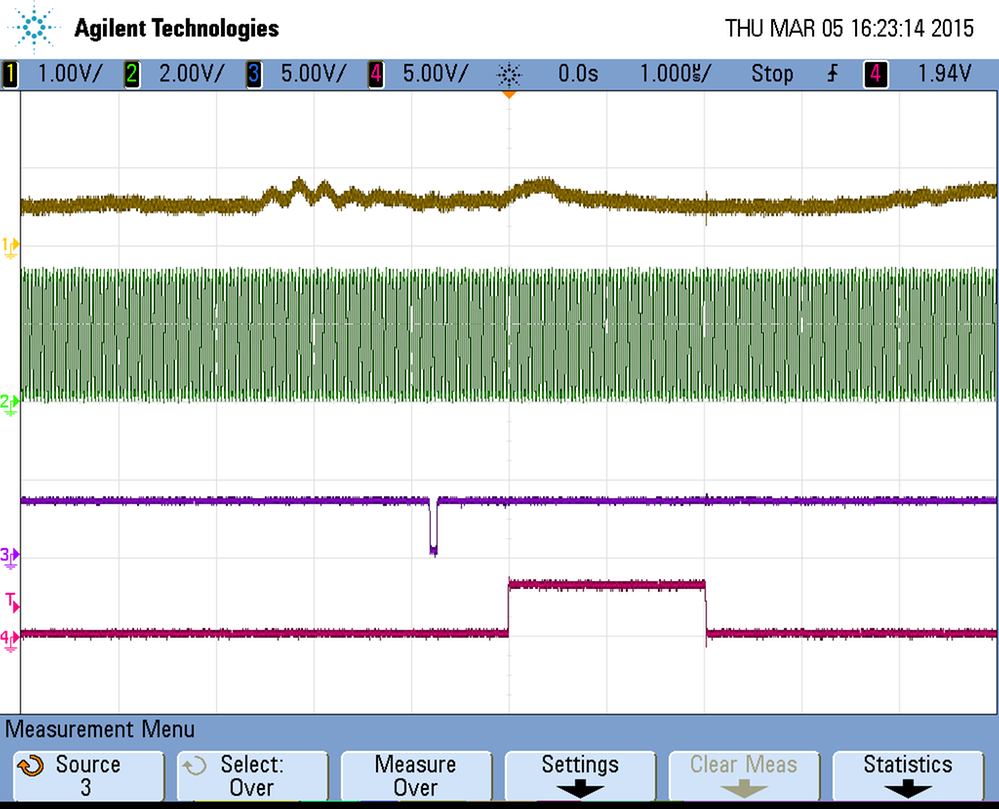

tested alignment on your board. Added pin output debug in VIU ISR.

So far: Field interrupt is not correctly aligned with start or end of the frame:

triggered at start of interrupt routine (peak at CH3 and 4 - trigger). Delay between start of frame and interrupt routine vary from about 300us to 6ms.

Decoding is not correct.

what is interesting it that interrupt comes always at same moment withing a line - in the middle of the line (probably latency). So we can say that it is between lines but not between correct lines:

ISR is alligned to HS from External ADC:

Ch4 is interrupt service routine, Ch3 is HS from external ADC

So wrong setting of Vybrid decoder, wrong setting of External decoder or wrong connection are valid reasons,..

/Jiri

Hi Sebastian,

we have checked all lines. If there are correctly connected to Vybrid: there is an issue on the board:

between External ADC and VIU data 2 is 10k resistor:

Measurement1:

Yellow is Analog

Red line is D2 (HR_VIU_DATA2) - before resitor

Green is clk

Light blue are D9 to D2

Red line is D2 (PTC2) - after resistor

So signal on D2 is not correctly connected.

Current state on terminal:

----------------------------------------------------------------------

Decoder Status (IN_LOCK): yes

Decoder Status (LOST_LOCK): no

Detected Video Standard: NTSC M/J

Correct line length detected: yes

Correct field length detected: yes

Interlaced video detected: yes

----------------------------------------------------------------------

Capture start !!!

VIU3 state is BUSY!

VIU3 state is BUSY!

VIU3 state is BUSY!

VIU3 state is BUSY!

VIU3 state is BUSY!

VIU3 state is BUSY!

VIU3 state is BUSY!

VIU3 state is BUSY!

VIU3 state is BUSY!

VIU3 state is BUSY!

Error stopping the VIU3 device, returned: 0xffffffff

VIU3 state is ERROR, error code is 47!

Device reset !!!

VIU3 state is READY!

Capture start !!!

VIU3 state is BUSY!

VIU3 state is BUSY!

...

...

We removed R604 and placed 0R - situation has changed significantly. signal on PTC2 is correct.

After resistor removal on terminal:

----------------------------------------------------------------------

Decoder Status (IN_LOCK): yes

Decoder Status (LOST_LOCK): no

Detected Video Standard: NTSC M/J

Correct line length detected: yes

Correct field length detected: yes

Interlaced video detected: yes

----------------------------------------------------------------------

Capture start !!!

VIU3 state is ERROR, error code is 7!

Device reset !!!

VIU3 state is READY!

Capture start !!!

VIU3 state is ERROR, error code is 5!

Device reset !!!

VIU3 state is READY!

Capture start !!!

VIU3 state is ERROR, error code is 5!

Device reset !!!

...

...

Error 7 is not enough lines

Error 5 is too many lines.

All interrupts are generated .

So now you have to change setting of the interface.

/Jiri

Sebastian,

VIU interrupt flags are w1c flags. Isn't it that you clear VSYNC_IRQ while trying to clear only FIELD_IRQ?

VIU3_SCR |= VIU3_SCR_FIELD_IRQ_MASK; // in fact clears ALL VIU3 interrupt flags.

proper way to clear only FIELD_IRQ flag would be this

VIU3_SCR = (VIU3_SCR & ~0x003F0000) | VIU3_SCR_FIELD_IRQ_MASK;

Edward

Dear Edward,

You are right. And our driver is doing it exactly this way ;-)

Problem is, that we didn't get an vsync-interrupt, even when we stop cpu using a jtag-debugger.

When cpu is in break-state we see in the viu registers that field-state toggles but there is never an vsync-irq.

Sebastian

Dear Timesys Support ,

May you help the customer from the "software point view”, please?

Thanks in advance, Naoum Gitnik.

timesyssupport can you help to attend this case?

Hello karinavalencia and naoumgitnik,

As noted in this other thread https://community.freescale.com/thread/321908 - we do not currently have a VIU driver in the Linux kernel. There may be efforts made in the kernel update we are working on to add one, but at this time, we can offer no in depth assistance in this matter.

Regards,

Timesys Support