- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- QorIQプロセッシングプラットフォーム

- :

- Tシリーズ

- :

- Re: T1024 L2Cache

T1024 L2Cache

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

T1024 L2Cache

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

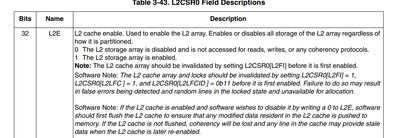

Need timing impact in setting and clearing of below bits by hardware. Will there be any variation in the timing with respect to environmental factor (temperature or electromagnetic effect).

1. After setting the L2IO and L2DO bits in L2CSR0, T1024 reference manual recommend the software to read these bits till it is set. The time taken to wait for setting L2IO and L2DO is consistent for hardware, or it will be changing with variation of environmental factor (temperature or electromagnetic effect) or any other factors?

2. After Setting L2FL bit to flush the cache, T1024 reference manual tells that bit will be cleared by hardware once the flush operation is done. The time taken to clear this bit by the hardware for fixed cache size will it be consistent or different at varying temperatures and environmental conditions?

3. After Setting L2FI bit to invalidate the cache, T1024 reference manual tells that bit will be cleared by hardware once the invalidate operation is done. The time taken to clear this bit by the hardware for fixed cache size will it be consistent or different at varying temperatures and environmental conditions

4. Setting the L2E bit in L2CSR0 and waiting for this bit to be set by hardware. The time taken to wait for setting L2E is consistent for hardware or it will be changing with variation of environmental factor (temperature or electromagnetic effect) or any other factors?

The Above information will be useful to understand deterministic and consistent hardware behavior for a considered Software.

If the time is varying, is there any factor how much it varies?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

we are not seeing any strange behavior, it is working as expected. we need to consider this for Worst Case execution time, we are waiting for these bits to be set or clear. The Variation in timing with respect to external factors (temperature or electromagnetic effect) need to be considered for WCET.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please refer to the following update from the AE team.

As I mentioned to you earlier we do not have any environment parameter correlation with wait time in our documentation. This means it is not a measured parameter that we have documented, So, I can not tell you the exact range of time nor environment interference impact on this time. So please tell customer that this is not a measured parameter that we have.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Appreciate your response in this regards, as you cannot provide the exact range could you tell us the temperature has performance impact on this? if not exact what could be the theoretical or approximate range?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Please refer to the following update from the AE team.

Per last reply, our documentation never suggested a correlation of time to finish with temperature.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Are you observing strange behavior?