- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: S32K344 LPSPI cs is active too long

S32K344 LPSPI cs is active too long

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S32K344 LPSPI cs is active too long

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

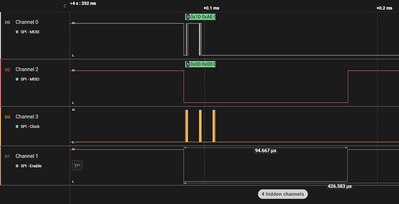

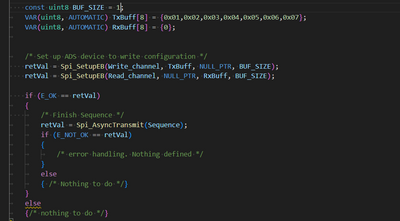

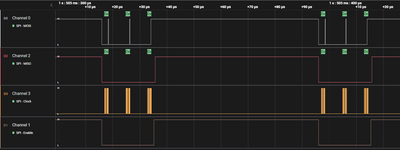

Hello. I am trying to work with SPI but have a problem . SPI transmission is too long. CS stays in active state after data is transferred.

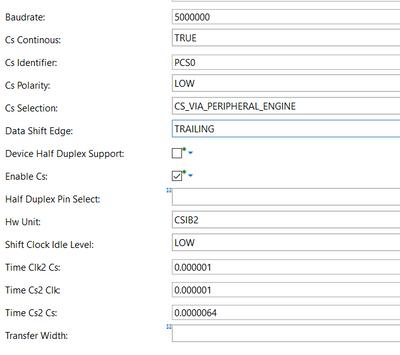

SPI configuration :

Has anyone encountered such behavior?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @VaneB . Thank you for the reply.

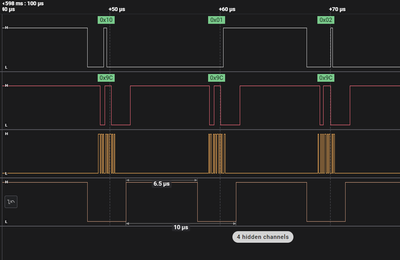

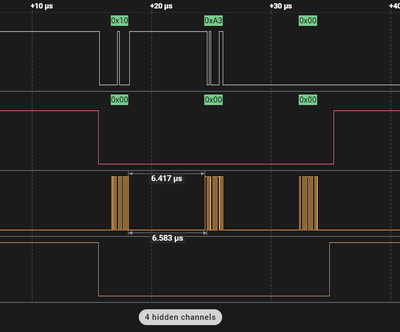

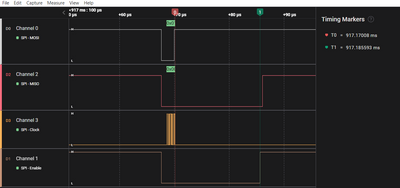

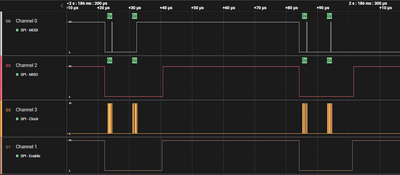

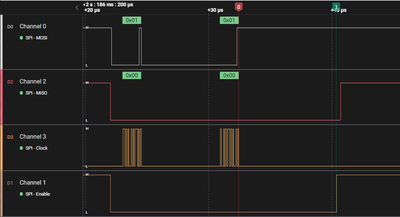

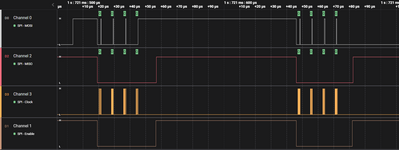

When I disable continuous transfer I have this timings.

but I need CS to be active during transferring all 3 bytes.

I have similar project and SPI configuration is the same but another behavior of CS.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @esmax

The platform should behave similarly by having the same LPSPI configuration so that the problem may be due to the implementation.

Could you tell me the differences in your projects to verify if this is the reason?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Actually there are no differences. I read SPI registers during debug. They look correct.

LPSPI_2/SR, 0x40360014, 0x00000001

LPSPI_2/CFGR0, 0x40360020, 0x00000000

LPSPI_2/CFGR1, 0x40360024, 0x00000001

LPSPI_2/CCR, 0x40360040, 0x27270000

LPSPI_2/CCR1, 0x40360044, 0xFF800303

According to datasheet there are no any SPI registers that can affect SPI behavior. Am I right ?

It is written that write operation to CCR register overwrites CCR1 but there is no information how CCR1 can be calculated.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @esmax

As I mentioned before the platform should behave similarly if it used the same LPSPI configuration for both projects.

I would like to know if you are using an EVB or a custom board. If you are testing each project on a different board. I would like to discard all possible causes of the problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using the same hardware

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @esmax

Since you are using the same hardware and the same LPSPI configuration in both projects, what must be generating this difference in CS behavior could be another module.

Could you help me with information regarding what other modules each project uses or if you want you can create a case in which you can share your projects with us so we can carry out tests.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello.

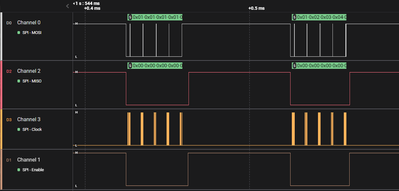

I use for the tests next code.

I do not change the code . Just size of buffers. As you can see I set up two buffers for transmission. They will be sent during one sequence.

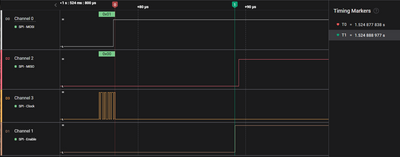

When the size of buffers equal to 1 I have a delay between transferring data and disabling CS is around 15 uS

When the size of buffers is 2 bytes a delay between transferring data and disabling CS is around 12 uS

When the size of buffers is 3 bytes a delay between transferring data and disabling CS is around 1 uS

When the size of buffers is 4 bytes a delay between transferring data and disabling CS is around 11 uS

When the size of buffers is 5 bytes a delay between transferring data and disabling CS is around 2.5 uS

When size of buffers 6 and 7 bytes, delays are the same as for 5 bytes length buffers.

Could you please tell me what can be a reason of such weird behavior of SPI ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @esmax

Could you verify if you have the same behavior with the example SPI_Transfer_S32K344 or Lpspi_Flexio_Ip_Transfer_S32K344?

Also, I notice that your clock is not symmetric, could you share an oscilloscope image of this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @esmax

Continuous Transfer configures to "keep PCS asserted between frames (as configured by FRAMESZ). A new command word is required to cause PCS to negate. Also supports changing the command word at the frame size boundaries."

If you disable continuous transfer you have the same behavior?

B.R.

VaneB