- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

I've got some problems with the LSPSI example.

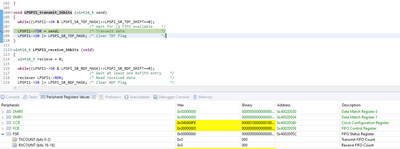

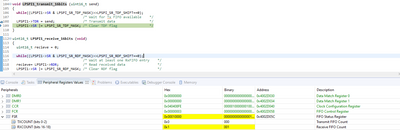

Before sending a SPI trame my TX and RX fifo counter are 0 .

After executing the ligne : LPSPI1->TDR = send; the RX counter has incremented to 1 but not the TX fifo counter ? Can someone explain me why ?

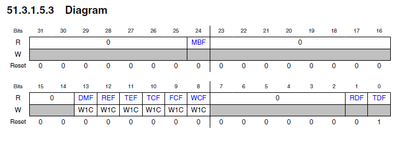

Besides that, I do not understand the ligne : LPSPI1->SR |= LPSPI_SR_TDF_MASK; /* Clear TDF flag */

Because in the RM, this bit seems not writable.

Thanks for your time and answers,

Florian

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Florian,

- The 16bit frame written to the TX FIFO goes to the TX shift register and is sent out. Meanwhile, an RX frame is received. That's why you see the frame in the RX FIFO but not in the TX FIFO.

- If you don't want to read the RX data, you can set the RXMSK bit in the command (TCR)

- Regarding the RDF, TDF clearing process, you are right, the example is not correct. The flags cannot be cleared by w1c.They get cleared automatically depending on the number of frames in the FIFOs and RXWATER / TXWATER thresholds.

BR, Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

I'm sending a SPI frame every second, the first start correctly but after few seconds, the RX fifo is full (nothing is connected on the SDIN pin) and the CS stay low after sending the last frame.

In the example, the flags cleared are in Read only mode, I still don't get it.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Florian,

- The 16bit frame written to the TX FIFO goes to the TX shift register and is sent out. Meanwhile, an RX frame is received. That's why you see the frame in the RX FIFO but not in the TX FIFO.

- If you don't want to read the RX data, you can set the RXMSK bit in the command (TCR)

- Regarding the RDF, TDF clearing process, you are right, the example is not correct. The flags cannot be cleared by w1c.They get cleared automatically depending on the number of frames in the FIFOs and RXWATER / TXWATER thresholds.

BR, Daniel

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Daniel,

Thanks for your answer, I understood I was receiving some frames on RX so I was reading them just to clear the RXFIFO. But the RXMSK bit you suggested seems to be a better option !

Thanks again

Florian