- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

S32K144 IIC communication question

Hello

I want to use the IIC fucntion of mcu s32K144,but I didn't want to use the process expert code to generate IIC function code.

After I configured these register,and initial the IIC register.I write the 0x04 command and one byte data to register MTDR, according to IIC communication protocal, then I should waite for transmission to end ,and check the ACK of slave device,for the ACK I check all register,and didn't have the ACK flag,so How can I judge the success of this send and start sending the next byte of data?

When IIC communciation occur error for sending address and data,The NACK flag will be detected,but this flag can't be the ending flag of sending data and address.I want to know that after send a data or address, I should check which register bit? and how I judge that this sending action has been finished,and I can send the next data.

Hello,

There is no such bit, you can fill the transmit FIFO with commands and data and expect ACK. "Multiple transmit and receive commands can be inserted between the START condition and STOP conditon; transmit and receive commands must not be interleaved..." (50.4.2.1 RM rev.9).

If NACK is received, the master will transmit a STOP condition and will not initiate a new START condition until NACK Detect Flag has been cleared. The transfer is complete when a Stop condition has been generated.

Regards,

Daniel

Hello

If I can check like this:after transfer a data,I check the bit TDF of register MSR,if the bit TDF is set as 1,I will think the transfer action has end?

I inintail the IIC function as below sequence:

uint32_t tmp = 0x00000000;

IIC_DRIVER_BASE->MCR = 0x00000002;

Delay_20us();

/**disable IIC**/

IIC_DRIVER_BASE->MCR = 0x00000000;

IIC_DRIVER_BASE->MSR = 0x00000000;

/***set clock Prescaler and diable match fucntion

***set pin fucntion and NACK

***/

IIC_DRIVER_BASE->MCFGR1 = 0x00000000;

/**set baud 100K**/

IIC_DRIVER_BASE->MCCR0 = 0x0D1A1A34;

/***disable all IIC interrupt**/

IIC_DRIVER_BASE->MIER = 0x00000000;

/**disable IIC DMA Fucntion**/

IIC_DRIVER_BASE->MDER = 0x00000000;

IIC_DRIVER_BASE->MCFGR0 = 0x00000000;

IIC_DRIVER_BASE->MCFGR2 = 0x00000000;

IIC_DRIVER_BASE->MCFGR3 = 0x00000000;

IIC_DRIVER_BASE->MDMR = 0x00000000;

IIC_DRIVER_BASE->MCCR1 = 0x00000000;

IIC_DRIVER_BASE->MFCR = 0x00000000;

/**enable IIC**/

tmp = (uint32_t)IIC_DRIVER_BASE->MCR;

tmp &= (uint32_t)(~(LPI2C_MCR_MEN_MASK));

tmp |= LPI2C_MCR_MEN(0x00000001);

IIC_DRIVER_BASE->MCR = tmp;

after executing the sequence,the valeu of register MSR is alway 0x02000001,so I can solve this issue?

Hello,

The MSR[TDF] flag is set whenever the number of words in the transmit FIFO is equal or less than TXWATER.

But all transfers begin with a START condition and are terminated by a STOP stop condition.

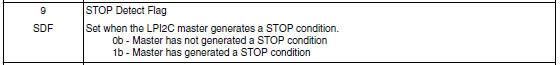

And there is a flag MSR[SDF] that is set whenever the master generates a STOP.

UM10204 I2C-bus specification and user manual.

Example_S32K144_I2C_Master_MPL3115A2_S32DSR1_v3

BR, Daniel

Hello,

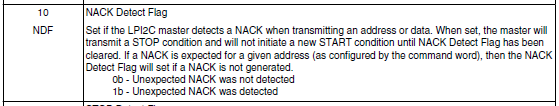

There is NACK Detect Flag in the Master Status register MSR[NDF] that is set whenever the master detects a NACK when transmitting an address or data.

When set, the master will transmit a STOP condition and will not initiate a new START condition until NACK Detect Flag has been cleared.

BR, Daniel