- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: Memset() with RAM segments

Memset() with RAM segments

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Memset() with RAM segments

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi NXP team,

I am using S32K144 controller in our project.

I used the meset() with linker script global variables.

memset(&__FSLCODE_SECTION_START, 0x00, __FSLCODE_SECTION_END - __FSLCODE_SECTION_START);

but that FSL code segment (section) is not set to zero.

find the attached document for more information on memeset() problem.

Regarding the watchdog timer :

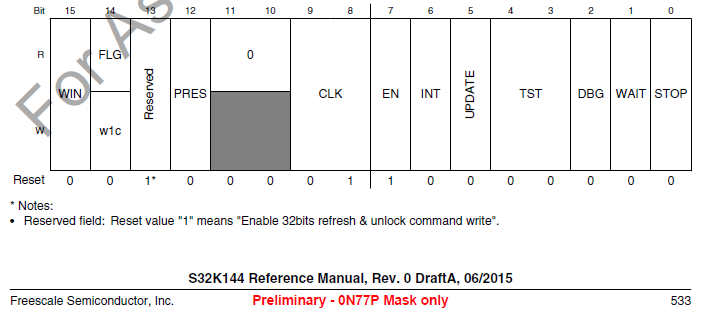

I used the code given in the reference manual for watchdog configuration

DISABLE_INTERRUPTS(); // disable global interrupt

WDOG->CNT = 0xD928C520; //unlock watchdog

while(((WDOG->CS & WDOG_CS_ULK_MASK) >> WDOG_CS_ULK_SHIFT) == 0); //wait until registers are unlocked

WDOG->TOVAL = 256; //set timeout value

WDOG->CS = WDOG_CS_EN(1) | WDOG_CS_CLK(1) | WDOG_CS_INT(0) |

WDOG_CS_WIN(0) | WDOG_CS_UPDATE(0);

while(((WDOG->CS & WDOG_CS_RCS_MASK ) >> WDOG_CS_RCS_SHIFT) == 0); //wait until new configuration takes effect

ENABLE_INTERRUPTS(); //enable global interrupt

if(WDOG->CNT >= 125)

{

DISABLE_INTERRUPTS(); // disable global interrupt

WDOG->CNT = 0xB480A602; // refresh watchdog

ENABLE_INTERRUPTS(); //

}

in the above code , control not come out of the while(((WDOG->CS & WDOG_CS_ULK_MASK) >> WDOG_CS_ULK_SHIFT) == 0);

Kindly help in this.

Regards,

Ambarish

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Raju,

//if(timeout_s > 127) return PUBLIC_STATUS_ERROR;

INT_SYS_DisableIRQGlobal();

WDOG->CNT = 0xD928C520; // Unlock WDOG

while(((WDOG->CS & WDOG_CS_ULK_MASK) >> WDOG_CS_ULK_SHIFT) == 0);

WDOG->TOVAL =timeout_ms;//128 * timeout_s; // Timeout in max = 65535 * (1 / 1 kHz) = 65535ms

//WDOG->CS = WDOG_CS_EN(1)|WDOG_CS_CLK(1)|WDOG_CS_INT(1)|WDOG_CS_WIN(0)|WDOG_CS_UPDATE(0);

WDOG->CS = WDOG_CS_EN(1) | WDOG_CS_CLK(1) | WDOG_CS_INT(0) | WDOG_CS_WIN(0) | WDOG_CS_UPDATE(0) | WDOG_CS_DBG(1);

while(((WDOG->CS & WDOG_CS_RCS_MASK ) >> WDOG_CS_RCS_SHIFT) == 0);

INT_SYS_EnableIRQGlobal();

It's stuck here

while(((WDOG->CS & WDOG_CS_RCS_MASK ) >> WDOG_CS_RCS_SHIFT) == 0);

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Wang,

If you are trying to update/ reconfigure the watchdog after initial watchdog configuration like initial disable watchdog function or something

I suggest you use WDOG_CS_UPDATE(1) in your initial watchdog configuration.

Raju

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Regarding the watchdog, the code works on my side with both masksets (0N47T, 0N57U) as expected.

There is a restriction that the reconfiguration must be done within 128 bus cycles.

So you cannot step the code.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@Hello Daniel,

Thank you for your support.

could you please share your complete tested source code.

I tried with toggling the LED while refreshing the watchdog , but LED is not toggling.

directly flashed the code and checked.

EVAL board has PS32K144HFVLL 0N77P controller chip.

PCC-> PCCn[PCC_PORTD_INDEX] = PCC_PCCn_CGC_MASK; /* Enable clock for PORT D */

PTD->PDDR |= 1<<0; /* Port D0: Data Direction= output */

PORTD->PCR[0] = 0x00000100; /* Port D0: MUX = ALT1, GPIO (to blue LED on EVB) */ WDOG->CNT = 0xD928C520; //unlock watchdog

DISABLE_INTERRUPTS();

while(((WDOG->CS & WDOG_CS_ULK_MASK) >> WDOG_CS_ULK_SHIFT) == 0); //wait until registers are unlocked

WDOG->TOVAL = 0x1E8480; // used the default clock configuration , not configured clock in the code //set the count to 2000000

WDOG->CS = WDOG_CS_EN(1) | WDOG_CS_CLK(1) | WDOG_CS_INT(0) |

WDOG_CS_WIN(0) | WDOG_CS_UPDATE(0);

while(((WDOG->CS & WDOG_CS_RCS_MASK ) >> WDOG_CS_RCS_SHIFT) == 0); //wait until new configuration takes effect

ENABLE_INTERRUPTS(); //enable global interrupt

while(1)

{

//PTD->PDDR = 1;

if(WDOG->CNT >= 0xF4240) //if count is equal or greater 1000000

{

DISABLE_INTERRUPTS(); // disable global interrupt

WDOG->CNT = 0xB480A602; // refresh watchdog

ENABLE_INTERRUPTS(); //

PTD->PTOR |= 1<<0;

}

}

Thanks,

Ambarish

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Ambarish,

The problem is in the maskset (0N77P).

Please use either 0N47T or preferably 0N57U which is the production version.

There are many differences between 0N77P and 0N47T/0N57U.

The current RM is not compatible with that maskset.

WDOG_CS[ULK] is not present on 0N77P thus it reads 0.

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

Is there any similar issue with S32K142.

Raju

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Raju,

No, there is no such issue with the S32K142.

There is only one S32K142 mask 0N33V covered by the S32K1xx RM, DS.

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

Thanks for the response.

I'm trying to implement the watchdog code and the code just has a while(1) loop with the below code. I expect the code will reset so I set a breakpoint at the start of the code to ensure the reset. But it still there is no reset happened.

DISABLE_INTERRUPTS();

WDOG->CNT = 0xD928C520; //unlock watchdog

while(((WDOG->CS & WDOG_CS_ULK_MASK) >> WDOG_CS_ULK_SHIFT) == 0); //wait until registers are unlocked

WDOG->TOVAL = 256; // used the default clock configuration , not configured clock in the code //set the count to 2000000

WDOG->CS = WDOG_CS_EN(1) | WDOG_CS_CLK(1) | WDOG_CS_INT(0) |

WDOG_CS_WIN(0) | WDOG_CS_UPDATE(0);

while(((WDOG->CS & WDOG_CS_RCS_MASK ) >> WDOG_CS_RCS_SHIFT) == 0); //wait until new configuration takes effect

ENABLE_INTERRUPTS(); //enable global interrupt

Kindly suggest us a solution

Raju.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Raju,

So the core stays halted at the breakpoint?

You can enable the WDOG in the debug mode of the MCU.

WDOG_CS[DBG] = 1

BR, Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Daniel. It is working now. Thanks for the support.

Raju