- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

Hi,

I am working on S32K144 LPUART. I want to test UART with 115200 baud rate for BLE connectivity. When configure baudrate as 115200kbps actual baud rate is 115384kbps.

When communicating only to BLE, communication is successful, once few task are added communication fails.

How to configure to 115200 exactly?

Thanks & Regards,

已解决! 转到解答。

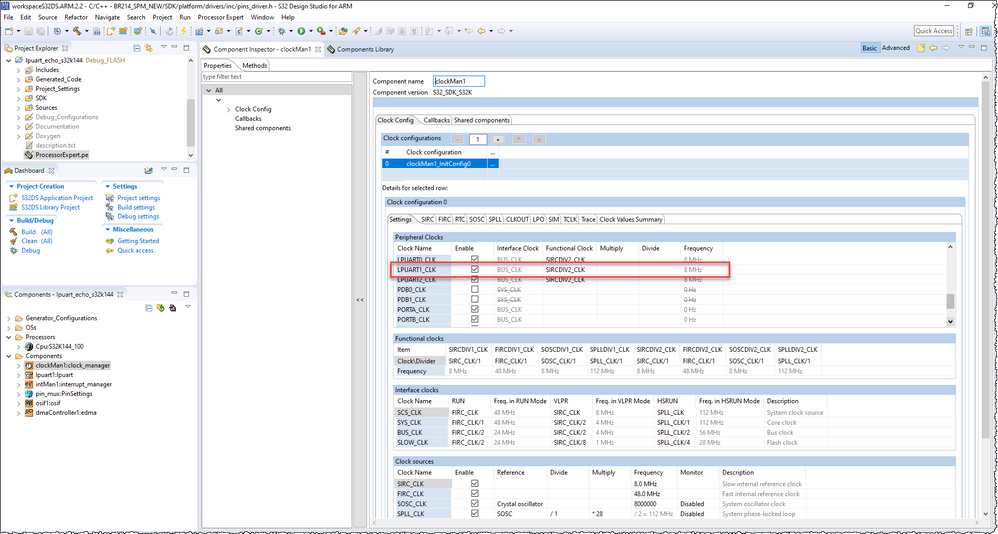

Thanks Robin. I measured and changed the baud rate. It is now working consistently. My problem has been solved by changing the LPUART0 clock to SIRCDIV2_CLK and by changing the Baud rate. Appreciate your help in getting it to work.

Best regards

Sandhya

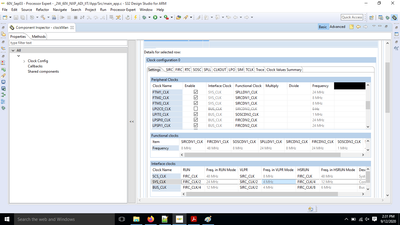

Thank you. After changing the clock for LPUART0 to SIRCDIV2_CLK, the BLE app is now connecting, but not consistently every time. It is successful 3 out of 5 times. What could be the reason? I am using LPUART1 with FIRCDIV2_CLK for USART interface, which is working fine. WIll this be affecting the behaviour of the BLE?

Please check the real baudrate of BLE.(Measure the bit width of signal sent out from BLE by using oscilloscope.)

You can adjust the baud rate of LPUART as close as possible to the baud rate of BLE.

You don't have to configure the baud rate of LPUART to 115200, just need to make the UART baud rate meet the tolerance require of BLE.

Best Regards,

Robin

Thanks Robin. I measured and changed the baud rate. It is now working consistently. My problem has been solved by changing the LPUART0 clock to SIRCDIV2_CLK and by changing the Baud rate. Appreciate your help in getting it to work.

Best regards

Sandhya

Hi sandhyaravikuma,

Would you please let me know the frequency of your BUS_CLK?

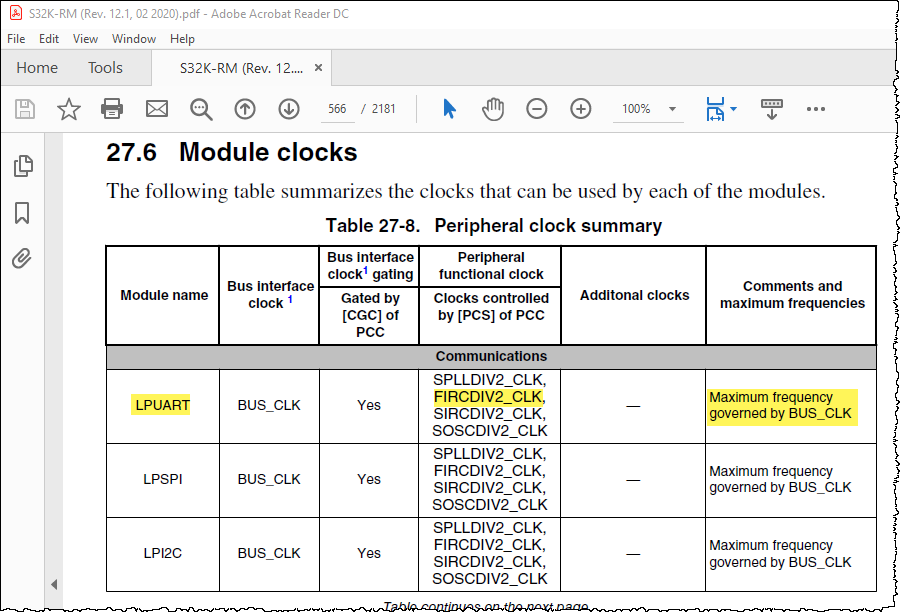

According to the "Table 27-8. Peripheral clock summary": Maximum frequency governed by BUS_CLK.

If the frequency of BUS_CLK is less than FIRC_DIV2(48MHz), then you can not use FIRC_DIV2 as the Peripheral functional clock of LPUART.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi sandhyaravikuma,

Have you try to measure the baud rate when communication fails?

Would you please tell me clock source of LPUART? The accuracy of the clock source will also affect the baud rate.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------