- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- Product Forums

- :

- S32K

- :

- Flex Memory Endurance calculator

Flex Memory Endurance calculator

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear NXP-Team,

I have difficulties to understand the calculations of the endurance of EEPROM.

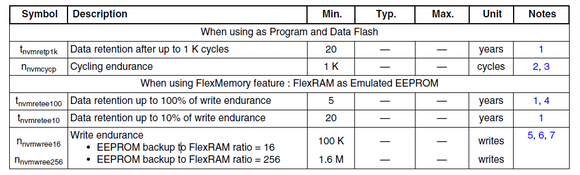

First we have the table from the data sheet:

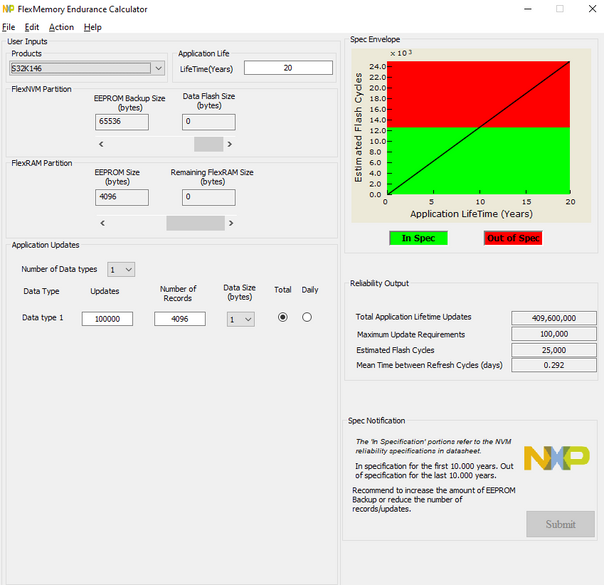

Second I have the output of the calculator:

I configured the calculator as follows:

65536B of EEPROM Backup size, 4096B of EEPROM size

--> I assume this should lead to a FLEXRAM ratio of 16.

I further more configure 4096 records with 1 byte each. In my book this should lead to 100k write cycles as indicated in the table above. However ... it does not.

I dont understand the section from green to red at 12.500 flash cycles. The table above indicates a max of 1.000 flash cycles

I furthermore dont understand the relation between 100.000 update requirements lead to 25.000 flash cycles. In my understanding, it should lead to 100.000/16 (ratio) = 6.250 flash cycles.

Could you please clarify my wrong understanding?

Kind regards

Stefan

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Stefan,

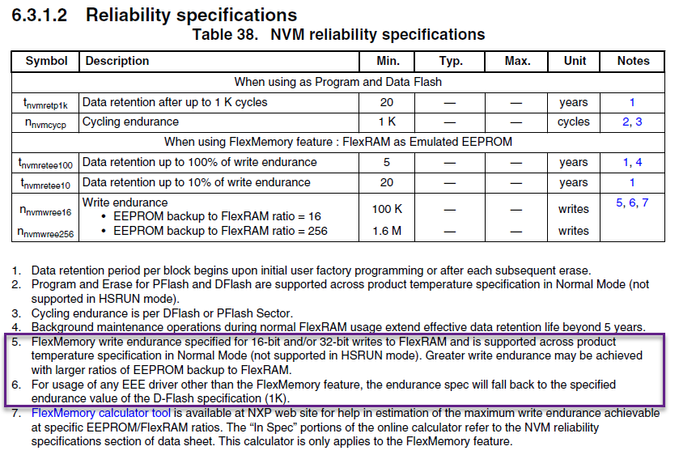

Please have a look at the footnotes in the table:

The 100k specification is for 16-bit and 32-bit writes only.

This is because one 8-bit record take the same amount of the EEPROM backup flash as one 16-bit record.

Thus the 25000 flash cycles in you example.

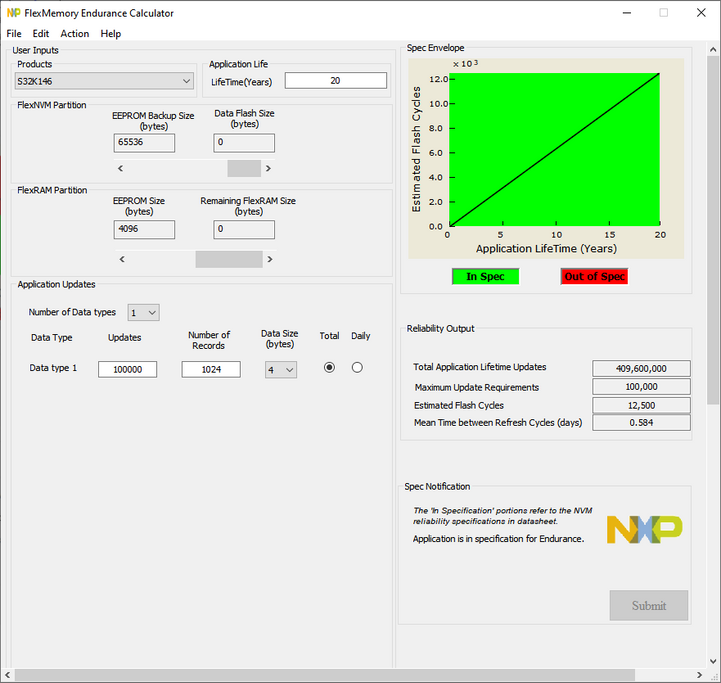

It is 12500 in the example below that uses 32-bit writes only.

Basically, the FlexNVM is more efficient in the Emulated EEPROM mode.

As the footnote 6 says, "For usage of any EEE driver other than the FlexMemory feature, the endurance spec will fall back to the specified

endurance value of the D-Flash specification (1K)."

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Daniel,

an additional question to FlexNVM endurance: Does it matter in which arrangement data is stored in the FlexRAM / Eeprom?

To get a (logical) separation of different data areas, I created 1kByte blocks in the eeprom in the linker script and distributed the eeprom data accordingly. Since this data never has a size of 1kByte, free areas remain between the individual blocks. Does this affect the lifetime of the FlexNVM?

For a better unterstanding see attached file "eeprom_layout.png"

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sebastian,

It does not matter:

"EEE writes don’t have to be to sequential location, indeed user can write to any valid location and/or write to the same address more than once."

AN11983 Using the S32K1xx EEPROM Functionality

Section 3.6.1 EEE writes

https://www.nxp.com/docs/en/application-note/AN11983.pdf

Regards,

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

@danielmartynekThanks a lot!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Stefan,

Please have a look at the footnotes in the table:

The 100k specification is for 16-bit and 32-bit writes only.

This is because one 8-bit record take the same amount of the EEPROM backup flash as one 16-bit record.

Thus the 25000 flash cycles in you example.

It is 12500 in the example below that uses 32-bit writes only.

Basically, the FlexNVM is more efficient in the Emulated EEPROM mode.

As the footnote 6 says, "For usage of any EEE driver other than the FlexMemory feature, the endurance spec will fall back to the specified

endurance value of the D-Flash specification (1K)."

Regards,

Daniel