- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32K

- :

- FTM clock source

FTM clock source

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

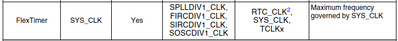

I have a really basic question about FTM clock source selection. In RM table 27-8 it is written:

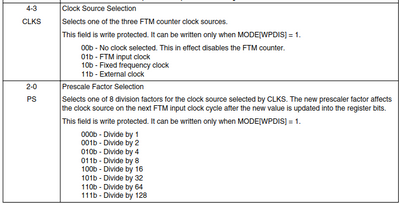

while in FTM_SC register the clock selection and prescaler is as follows:

The board is configured to run at system clock of 80 MHz and SPLLDIV1_CLK is set to 10 MHz (division factor of 16 from 160 MHz SPLL).

So my question is if according to the first snapshot the FTM clock source is selected to be SPLLDIV1_CLK and therefore it should run at 10 MHz, how does this relate to the second snapshot where the clock can be selected to be FTM Input clock? What is FTM Input clock in this case? Does it refer to the same 10 MHz SPLLDIV1_CLK?

In AN5303 it is mentioned that FTM clock source for counter can be either system clock, the fixed frequency clock or external clock. This apparently corresponds to the second snapshot above, but again how then the first snapshot is used to configure FTM clock source?

Still another question regarding the first snapshot. The second column for FlexTimer clock is SYS_CLK, while the forth column has other clocks like SPLLDIV1_CLK, FIRCDIV1_CLK, etc. Does the second column mention just the maximum possible clock? Or is there some other purpose?

I guess, all the above questions relate to some basic misunderstanding from my side of how FTM source clock (counter clock) is selected.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi davithakobyan,

Yes. Your understanding is correct.

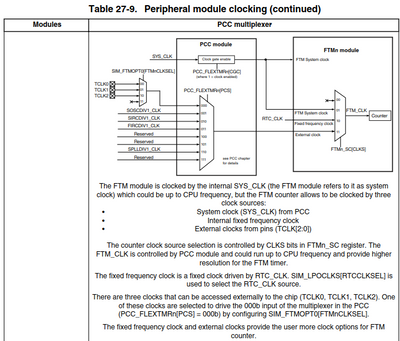

Due to FTMn_SC[CLKS]=01 select 80MHz FTM System clock, so the PCC_FLEXTMRn[PCS]=110 selected SPLLDIV1_CLK will not clock the FTM module.

Best Regards,

Robin

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Ok, it seems the answer is given in the next diagram:

So the SPLLDIV1_CLK clock will be used by FTM counter only if the external clock source is selected for the FTM module. If the system clock is still selected then FTM counter will still run at 80 MHz despite the selection of SPLLDIV1_CLK in PCC module.

Please correct if the diagram has a different interpretation.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi davithakobyan,

Yes. Your understanding is correct.

Due to FTMn_SC[CLKS]=01 select 80MHz FTM System clock, so the PCC_FLEXTMRn[PCS]=110 selected SPLLDIV1_CLK will not clock the FTM module.

Best Regards,

Robin

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------