- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- S32K

- :

- Re: ADC High Sampling Rate and Graph

ADC High Sampling Rate and Graph

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I'm using S32K144 with S32DS. I want to use the ADC function with a very high sampling rate to capture a high frequency signal. What is the maximum sampling frequency I could achieve using this board?

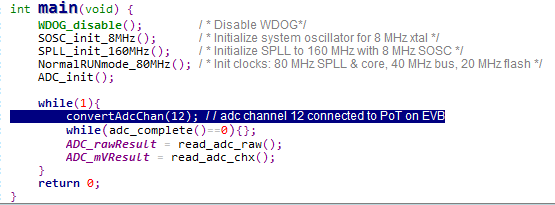

I have already have coded ADC with SWTrigger mode (using the example code), and changed the PCC->PCCn[PCC_ADC0_INDEX] |= PCC_PCCn_PCS(6); to use the high frequency SPLL clock. Also, reduced the ADC0->CFG2 = 0x000000002; to reduce the sampling time.

Does this mean the ADC is sampling at 80MHz? Please check the attached code and let me know.

My next step is to get the ADC values and plot a graph using those values. It would be of great help if anyone could tell me a way to do that.

Any help is appreciated.

Thanks.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sadab,

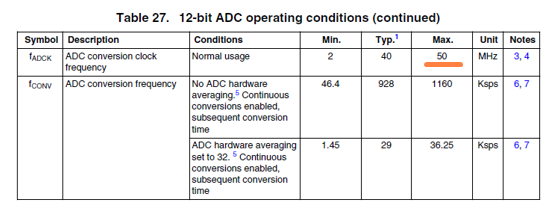

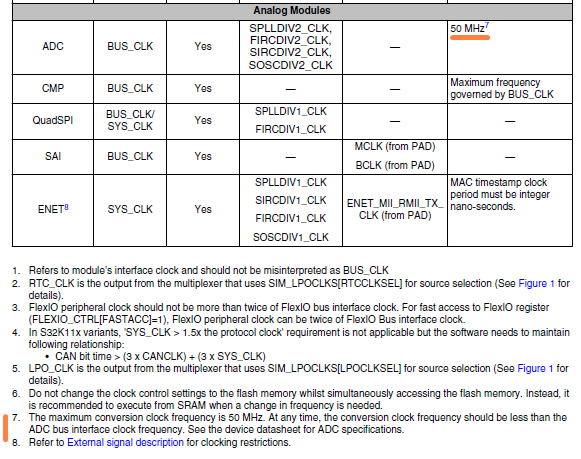

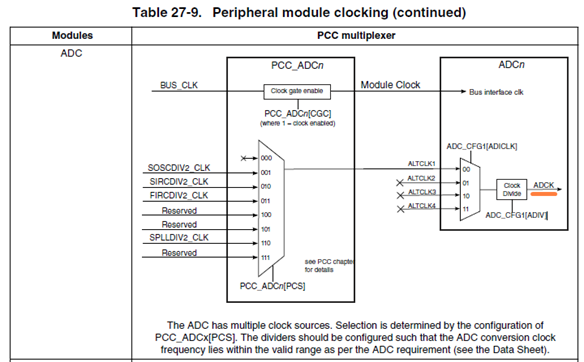

The ADC conversion clock frequency ADCK is limited to 50MHz.

The peripheral clock selected in PCC_PCS is divided by ADC_CFG1[ADIV].

Please see below specifications.

If you want to sample one ADC input continuously, you can select continuous conversion ADC_SC3[ADCO] and use DMA to transfer the results to RAM.

Or you can use PDB to trigger a sequence of conversion in back-to-back mode and again use DMA.

You can plot a graph from the results in RAM.

You can refer to this example:

https://community.nxp.com/docs/DOC-333054

Regards,

Daniel

S32K1xx Datasheet rev.9

S32K1xx Reference Manual rev.9

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Sadab,

The ADC conversion clock frequency ADCK is limited to 50MHz.

The peripheral clock selected in PCC_PCS is divided by ADC_CFG1[ADIV].

Please see below specifications.

If you want to sample one ADC input continuously, you can select continuous conversion ADC_SC3[ADCO] and use DMA to transfer the results to RAM.

Or you can use PDB to trigger a sequence of conversion in back-to-back mode and again use DMA.

You can plot a graph from the results in RAM.

You can refer to this example:

https://community.nxp.com/docs/DOC-333054

Regards,

Daniel

S32K1xx Datasheet rev.9

S32K1xx Reference Manual rev.9

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you Daniel.

I used the PDB triggering in back-to-back mode to get ADC inputs from 2 or more channels. Did not implement the DMA yet, but I'm working on it.

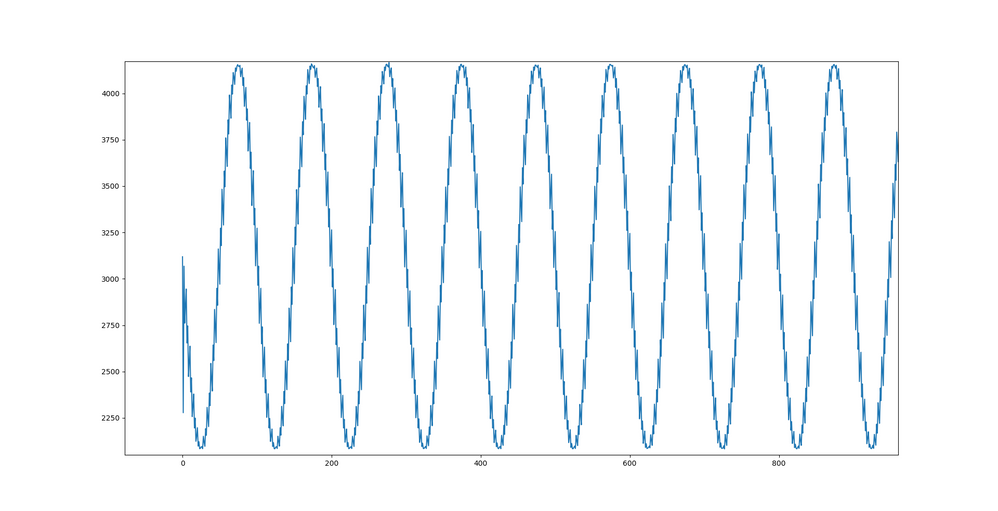

I set the sampling rate at 40MHz and set up LPUART to transfer the recorded data at 115200 baud rate via PuTTY then, used python to plot graphs.

I was pretty satisfied with the data that I collected, the graph looks pretty decent.

Here's a graph of a sine wave at 500Khz.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello,Are you in continuous mode? Whether continuous mode is suitable for back to back?

my app needs to 24 channel adc.but i can't improve Sampling Rate。

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, sorry for the late reply. I didn't notice the notification.

I guess I am not using the continuous mode. For PDB back-to-back you need HW trigger.

For greater sampling rate you need to select the SPLL clock as source in PCC_PCCn_PCS, and then look into the CFG1 and CFG2 registers for sampling time calculation.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I tried to understand which parameters of ADC_CFG1 and ADC_CFG2 but with no result. I need to improve my sample rate to achieve one sample per bit in 500 kbps CANH and CANL channels. Does anyone know how to do it?

Kindly guide me or small example code will be helpful. Many thanks

Andrea

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear . Sadab Mahmud

I also under studding ADC high sample Rate.

I think convertAdcChan(12); was change like below.