- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

9 Bit SPI with DMA

I need to interface display with S32K142 MCU.

My project hardware has only 3 wires (CSX, SDA and SCL) from the display side. I have to use 3-wire 9-bit mode only.

So I changed SDK for 3 wire SPI configuration according to reference manual.

So this is my MasterInit Function and I configured SDO pin as Input/Output.

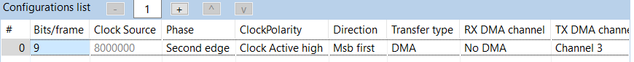

And processor expert configuration is depicted below.

and this is my function

If so, I would like to know how to send 9 bits (1 D/C bit + 8 data bits) using SPI APIs. MasterGetTransferStatus function returned STATUS_BUSY. Is there any error?

How should I do that process. Thanks for answering.

Hi @maximillion

Changes can be made to make the SDK functions support half-duplex.

As mentioned in the reference manual, to configure LPSPI in a half-duplex it is required to define CFGR1[PINCFG] as 01b (SIN is used for both input and output data) or 10b (SOUT is used for both input and output data), CFGR1[OUTCFG] as 1b to configure to tristate when LPSPI_PCS is negated and depending of the implementation for 2-bit transfers CFGR1[PCSCFG] as any value or for 4-bit transfers as 1b.

If we see from the SDK, LPSPI_SetPinConfigMode() needs to configure SDI as LPSPI_SDI_IN_OUT or SDO as LPSPI_SDO_IN_OUT and LPSPI_DATA_OUT_TRISTATE. These modifications would be for the register CFGR1 that I mentioned before.

For more reference, the post I shared earlier talks about the situation with no SDK.

Hi @VaneB

I have to use SDK so according to your last post my 3-wire SPI configuration is true right?

First of all, I used DMA for SPI configuration via Processor Expert. So I have a question about this topic. I used LPSPI_DRV_MasterTransfer() functions and LPSPI_DRV_MasterGetTransferStatus() to send SPI data. There are 4 parameters in LPSPI_DRV_MasterTransfer().MasterTransfer function, one of them is receiveBuffer but I am using 3-wire SPI so I gave NULL parameter for receiver buffer. Is this valid? If yes how can I get data from slave device via txBuffer. Is this possible for the RTM3.0.0 SDK?

Secondly, does the LPSPI_DRV_MasterTransfer function need to be modified to send and receive data on the same DMA TX channel? Because I choose No DMA for Rx channel via processor expert.

I am not totally clear about this sentence "when LPSPI_PCS is negated" what does that mean "PCS negated". Isnt peripheral chip select value low right?