- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- Home

- :

- Product Forums

- :

- S32G

- :

- Divider configuration update is pending for CLKOUT0

Divider configuration update is pending for CLKOUT0

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am trying to generate an clock out of 1MHz on CLKOUT0 on S32G274A with the below configuration but divider configuration update is pending continuously.

MUX_1_CSC : SELCTL -- clk_src_2, FCG -- 0, CG -- 1

MUX_1_DC_0 : DE -- 1, DIV -- 0x27

MUX_1_DIV_UPD_STAT : 1

Please let me know as how to resolve this issue.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

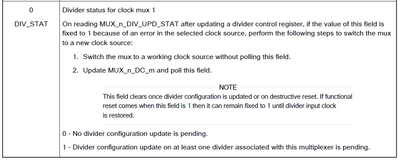

Thanks for your feedback. Seen the S32G2 RM, we found the following note [Page 979, S32G2 Reference Manual, Rev. 7, February 2023]:

Which mentioned that if the DIV_STAT bit stays at 1, then the problem might be related to the selected clock source, and 2 steps are shown on how to change if that happens.

As for the configuration the mux itself, we see that Figure 130 and 131 under the RM [Page 1161 & 1163, S32G2 Reference Manual, Rev. 7, February 2023] show the expected flow to configure the CLK switch, we understand that not all steps are being followed under the pseudo-code shared with us.

Can you confirm that following the steps provide a different outcome?

Please, let us know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Which RTD version are you using? For what we can see, you might not be using one, but we would like confirmation.

Also, are you using any NXP development board? Or is this a custom board?

Please, let us know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am not using any packages of drivers, its my own piece of code. Testing is done on NXP development board S32G-VNP-RDB2 REVC.

I hope i have answered your question correctly.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your feedback. Seen the S32G2 RM, we found the following note [Page 979, S32G2 Reference Manual, Rev. 7, February 2023]:

Which mentioned that if the DIV_STAT bit stays at 1, then the problem might be related to the selected clock source, and 2 steps are shown on how to change if that happens.

As for the configuration the mux itself, we see that Figure 130 and 131 under the RM [Page 1161 & 1163, S32G2 Reference Manual, Rev. 7, February 2023] show the expected flow to configure the CLK switch, we understand that not all steps are being followed under the pseudo-code shared with us.

Can you confirm that following the steps provide a different outcome?

Please, let us know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel,

The steps mentioned in Figure 130 and 131 under the RM [Page 1161 & 1163, S32G2 Reference Manual, Rev. 7, February 2023], has supported to resolve the issue.

Thanks a lot.