- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

-

- Home

- :

- ソフトウェア・フォーラム

- :

- S32 SDK

- :

- S32K148 LPSPI transfer error

S32K148 LPSPI transfer error

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

S32K148 LPSPI transfer error

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi NXP community,

I have a problem with the LPSPI0 transfers which explain below.

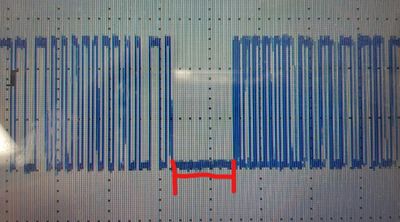

When I set LPSPI0 as master to transmit 4 bytes at 4,8MBaudrate with LPSPI0_CLK_SEL = 24MHz (FIRCDIV2 / 2), there seems to be a pause in the middle of the 4 bytes I’m sending.

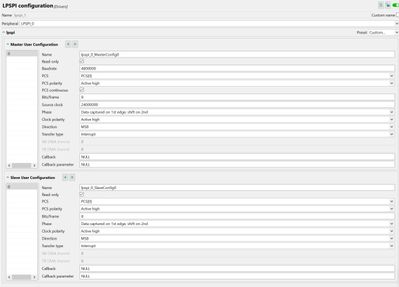

The applied settings can be seen in the following images.

To isolate the problem as much as possible I have done a project that only sets LPSPI0 as master and makes an infinite loop that only makes transmissions and waits.

If you need to clarify anything about the management or configuration I do in the LPSPI interface, please let me know.

Best regards,

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello @FBS,

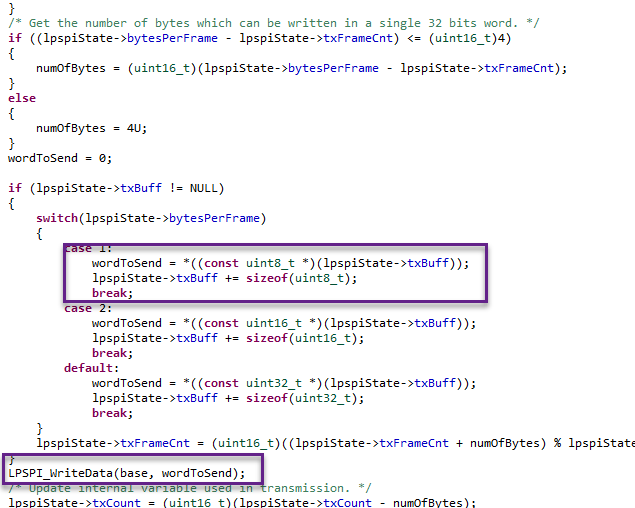

If you configure the SDK LPSPI for 8bit frames, in the interrupt mode, the LPSPI_DRV_FillupTxBuffer() function (lpspi_shared_function.c) that is called from the interrupt handler can fill the TX FIFO with 8bit frames. The FIFO can take only up to 4 such frames.

The SDK LPSPI driver needs some time to fill the TX FIFO (CPU overhead).

You can reduce the delay either by increasing the system clock frequency or by reducing the SPI bitrate.

Regards,

Daniel