- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 製品フォーラム

- :

- S12 / MagniVマイクロコントローラ

- :

- There meet a question about HCS12 Chip's SCISR1Register

There meet a question about HCS12 Chip's SCISR1Register

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

There meet a question about HCS12 Chip's SCISR1Register

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

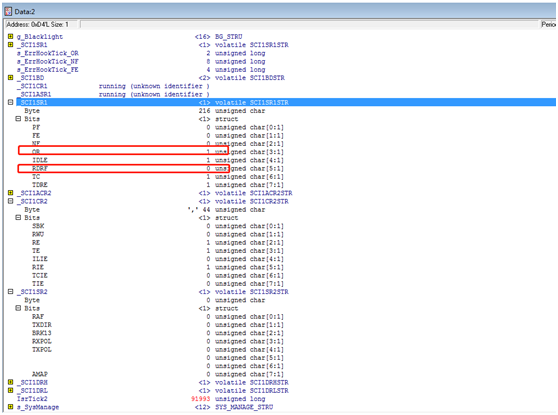

When I debug my uart process,I found my uart process runs unusual.

Then I found the SCISR1's OR bit can not be clear and set with out RDRF bit set.

Usual when RDRF bit and OR bit set at the same time I can clear them all by read scisr1 regiser and scidrl

But I check datasheet I can't find the discrib about this abnormal situation.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hello,

Does this problem appear only in the case of debugging?

Unfortunately, you did not specify the concrete MCU.

So, at first, I would like to recommend you to look at the similar threads available on the community:

Debuuging SCI RDRF bit in Codewarrior

For example, If you have S12G MCU you can find the description OR flag in the Reference Manual rev. 1.27:

"Note: OR flag may read back as set when RDRF flag is clear. This may happen if the following sequence of

events occurs:

1. After the first frame is received, read status register SCISR1 (returns RDRF set and OR flag clear);

2. Receive second frame without reading the first frame in the data register (the second frame is not

received and OR flag is set);

3. Read data register SCIDRL (returns first frame and clears RDRF flag in the status register);

4. Read status register SCISR1 (returns RDRF clear and OR set).

Event 3 may be at exactly the same time as event 2 or any time after. When this happens, a dummy

SCIDRL read following event 4 will be required to clear the OR flag if further frames are to be received."

I hope it helps.

Best Regards,

Diana