- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- S12 / MagniV Microcontrollers

- :

- S12G SPI polarity control

S12G SPI polarity control

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

S12G SPI polarity control

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The SPI MOSI pin defaults to high. So when no data is being sent, it goes high. I would like it to be low.

So I had a look at the Port Integration section of the Reference Manual, and it seemed this should be possible. The settings would be: wire-or mode, pull enabled, pulldown i.e. for MOSI on port 0:

WOMS &= ~0b00100000; // set PS5 to wire-or mode

PERS |= 0b00100000; // enable pull resistor on PS5

PPSS |= 0b0010000; // pull down

I'm afraid this doesn't work. I assume that is because these configuration bits do not apply when using the pins as SPI.

Or have I made an error?

Any other way to make the default state of MOSI low?

TIA

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

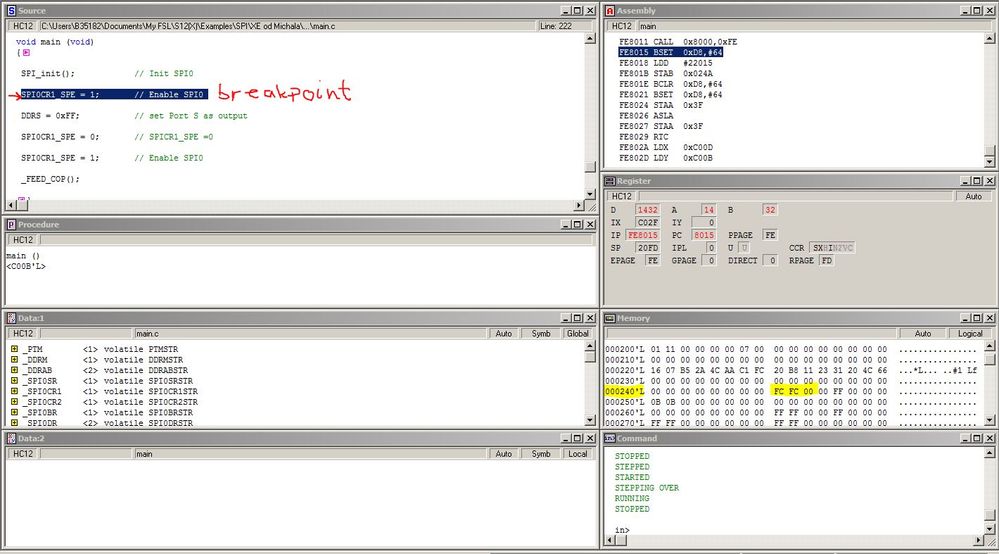

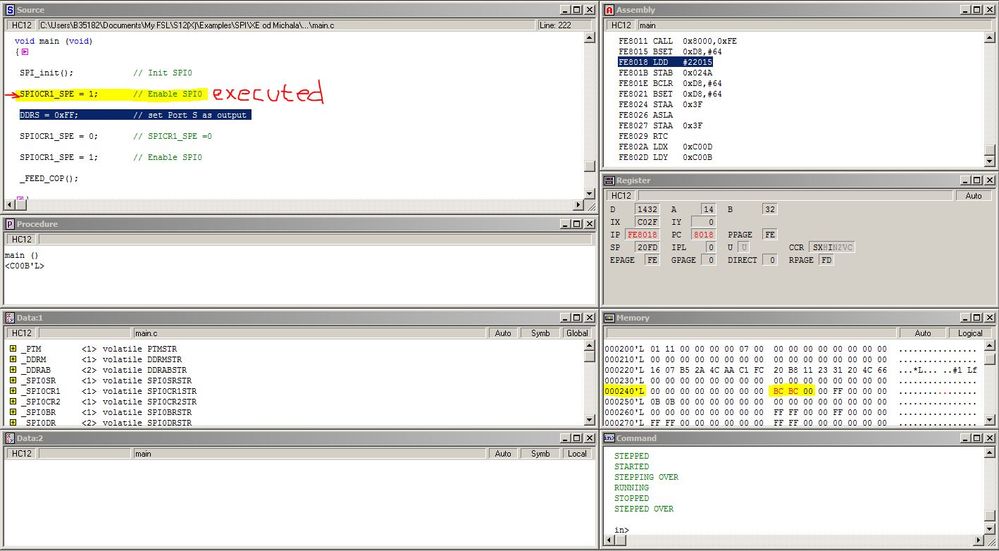

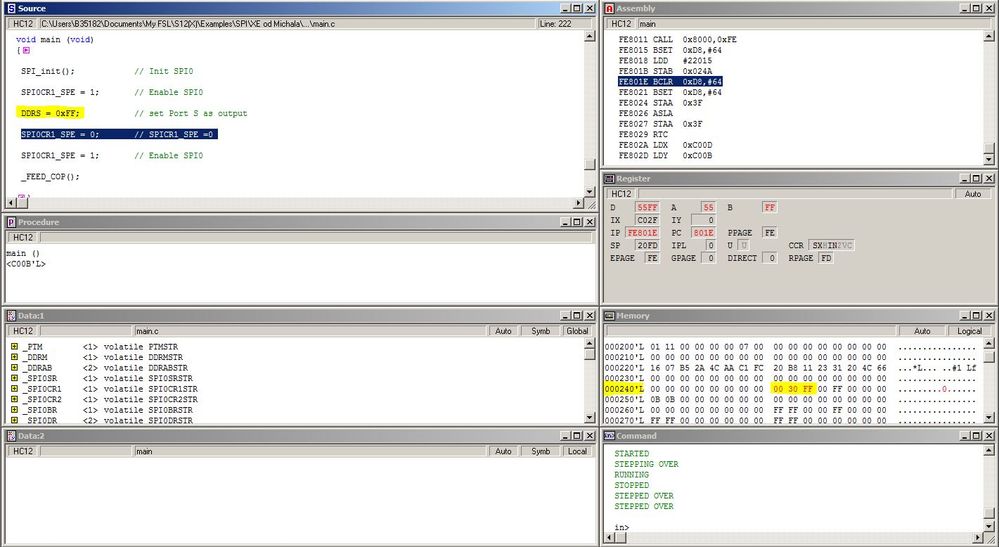

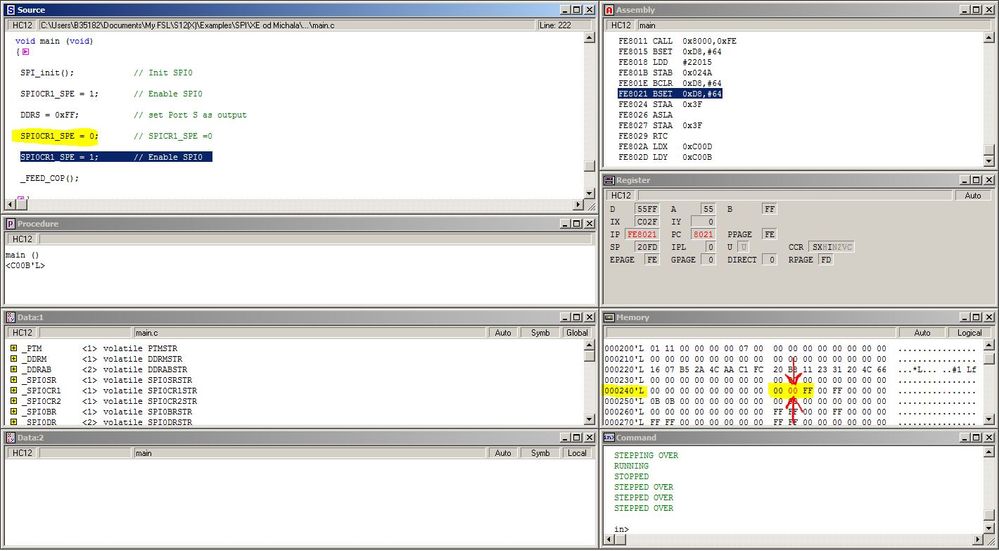

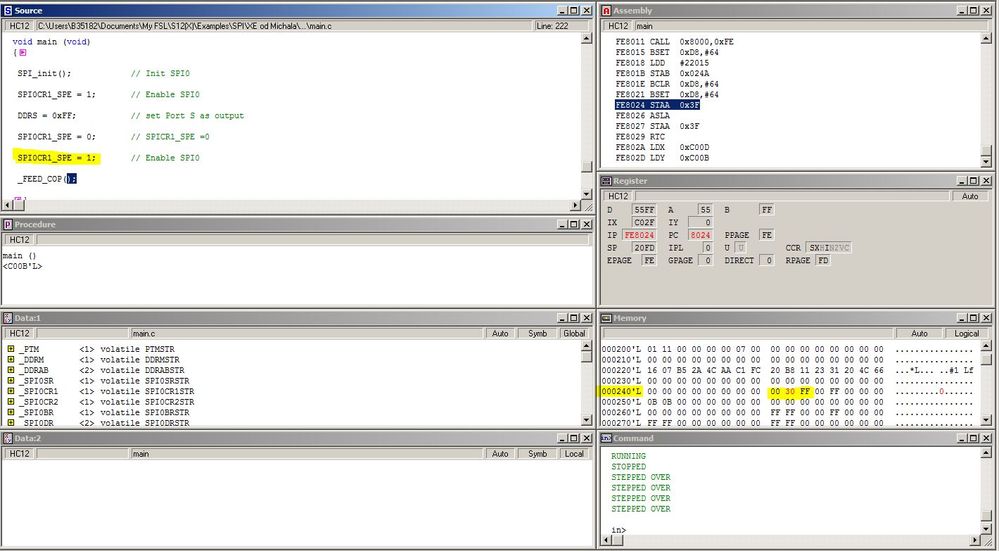

David is right. You must disable the SPI. Also you should set the Port Data Direction Register (DDRS for example) as output. I've tested this on DEMOAX9S12XEP100 board. See screenshots below (click on them to enlarge):

1. Initial state. SPI module initialized, but not enabled yet. The yellow marked address in memory window shows Port S Data Register (PTS) at 0x0248, Port S Input Register (PTIS) at 0x0249 and Port S Data Direction Register (DDRS) at 0x024A address.

As you can see Port S is set as input and PTIS reflects the buffered state on the pin which is 0xFC (taken from the PTS register). The MOSI pin (PS5) is logic 1.

2. SPI enabled. Port S dedicated to SPI module.

3. Port S set as output. SPI still enabled. the PTIS reflect the 4 SPI pin status: MOSI and MISO are high.

4. SPI disabled. Finally, PS5 (MOSI) pin is low as well as other Port S pins.

5. SPI enabled again. Doublecheck the Port S status. MOSI/MISO pins are high again.

Regards,

iggi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In SPICR1 after your SPI session is complete, set SPE to 0. This will take SPI off the buss and allow IO control over the pin.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello,

how have you configure the SPI module (SPICR1, SPICR2, SPIBR...) ?

your problem must be in the configuration of the module.