- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

Hi,

Our development board using p2020 needs to support 4G SDRAM. So we need CONFIG_36BIT enable.

In board.cfg, we add our config like

Status, Arch, CPU:SPLCPU, SoC, Vendor, Board name, Target, Options,

Active powerpc mpc85xx - freescale develop-1 DEVELOP-1 -

Active powerpc mpc85xx - freescale develop-1 DEVELOP-1_36BIT develop-1:36BIT

Q1: we have a develop-1.h under include/configs/ and folder develop-1 under board/freescale/. As I know the options format <board>:[other options], so I setting develop-1:36BIT. Is it correct??

Q2: we add DEVELOP-1 first and then DEVELOP-1_36BIT. If we want to build DEVELOP-1_36BIT, should we need to type from "bitbake -c cleansstate u-boot" or what command can we use to save our time build new configuration?? For example, bitbake -c clean <target>, bitbake -c cleansstate <target>, bitbake -c cleanall <target>.

At last, we using boot code not support 36BIT in our board which have a 4G SDRAM, then we see.

Not enough bank(chip-select) for CS0+CS1 on controller 0, interleaving disabled!

Detected 4 GiB of memory

This U-Boot only supports < 4G of DDR

You could rebuild it with CONFIG_PHYS_64BIT

2 GiB (DDR3, 64-bit, CL=6, ECC off)

Thanks for any response.

Best Regard,

Kuowei Hsu

已解决! 转到解答。

Hello Kuowei Hsu,

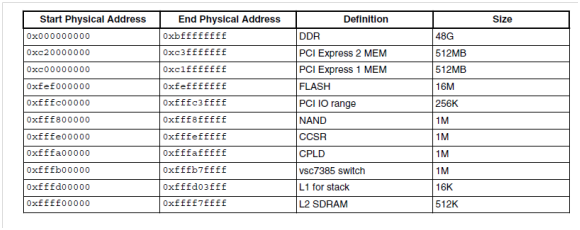

In SDK 1.6, P2020RDB supports 36bit u-boot, please refer to the follow 36 bit memory map.

For u-boot customizing for your target, please check whether the following steps would be better.

1. Clean u-boot Cache and get u-boot source code.

$ bitbake -c cleansstate u-boot

$ bitbake -c patch u-boot

2. Go to u-boot source folder build_p2020rdb_release/tmp/work/p2020rdb-fsl-linux-gnuspe/u-boot/2014.01+fslgit-r0/git/ to modify the source file.

Please modify these files according to your target board.

include/configs/P1_P2_RDB.h

Files in board/freescale/p1_p2_rdb_pc/, for example ddr.c, law.c, tlb.c.

3. The u-boot configuration P2020RDB-PC_36BIT has already been defined in meta-fsl-ppc/conf/machine/p2020rdb.conf

4. Rebuild U-Boot image

$ cd build_p2020rdb_release

$ bitbake -c compile -f u-boot

$ bitbake u-boot

If further assistance is needed, please feel free to let me know.

Have a great day,

Yiping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hello Kuowei Hsu,

In SDK 1.6, P2020RDB supports 36bit u-boot, please refer to the follow 36 bit memory map.

For u-boot customizing for your target, please check whether the following steps would be better.

1. Clean u-boot Cache and get u-boot source code.

$ bitbake -c cleansstate u-boot

$ bitbake -c patch u-boot

2. Go to u-boot source folder build_p2020rdb_release/tmp/work/p2020rdb-fsl-linux-gnuspe/u-boot/2014.01+fslgit-r0/git/ to modify the source file.

Please modify these files according to your target board.

include/configs/P1_P2_RDB.h

Files in board/freescale/p1_p2_rdb_pc/, for example ddr.c, law.c, tlb.c.

3. The u-boot configuration P2020RDB-PC_36BIT has already been defined in meta-fsl-ppc/conf/machine/p2020rdb.conf

4. Rebuild U-Boot image

$ cd build_p2020rdb_release

$ bitbake -c compile -f u-boot

$ bitbake u-boot

If further assistance is needed, please feel free to let me know.

Have a great day,

Yiping

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------