- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

UJA1169ATK/F V1 undervoltage reset

Hello, we use battery to supply VBAT(6.66V~7V), V1RTSUC is 80% and V1RTC is 90%, then SBC will reset, and RSS in Main status register(03h) will return 10011(V1 undervoltage).

Increase the voltage on VBAT to 8V, the temperature will influence V1: UJA1169 will be OK below 65℃;while it will reset due to V1 undervoltage above 65℃.

When VBAT is 13V, the SBC is OK.

So, why VBAT and temperature will result in V1 undervoltage?

HI.guoweisun

I would like to ask a technical question about the UJA1169A, and since I didn't find a way how to post a new thread, this is the only way I can ask you.

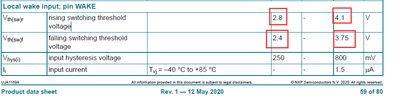

As shown in the figure below, Vth(sw)r is the threshold for the rising edge from a low level to a high level, and Vth(sw)f is the threshold for the falling edge from a high level to a low level, why is there an intersection between these two thresholds?2.8V is contained within 3.75VHow is this understood?

For the UJA1169A, can the WAKE pin be internally configured with a pull-up or pull-down circuit? If the input signal is active low, must the WAKE pin have a resistor pull-up circuit?

HI.guoweisun

I would like to ask a technical question about the UJA1169A, and since I didn't find a way how to post a new thread, this is the only way I can ask you.

As shown in the figure below, Vth(sw)r is the threshold for the rising edge from a low level to a high level, and Vth(sw)f is the threshold for the falling edge from a high level to a low level, why is there an intersection between these two thresholds?2.8V is contained within 3.75VHow is this understood?

For the UJA1169A, can the WAKE pin be internally configured with a pull-up or pull-down circuit? If the input signal is active low, must the WAKE pin have a resistor pull-up circuit?