- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Power Management

- :

- Power Management

- :

- Re: LBIST issue with MC33FS6500LAE

LBIST issue with MC33FS6500LAE

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @AllanAn ,

One of customer is facing below issue with regards to MC33FS6500LAE PMIC :

- During first power up, all of the voltage rails (Vpre,Vcca,Vaux) show an under-voltage bit being set in diagnostic registers- ONLY first time read. Subsequently when the registers are read there is no under-voltage that is set (except VAUX- this is expected as VAUX is not being used). Why do we see initial under voltage in all voltage rails ?

- The LBIST fault remains to show in the BIST Register every time the register is being read.

We are not able to determine the reason for the LBIST error as no such clear causes are mentioned in the documentation with regards to the chip.

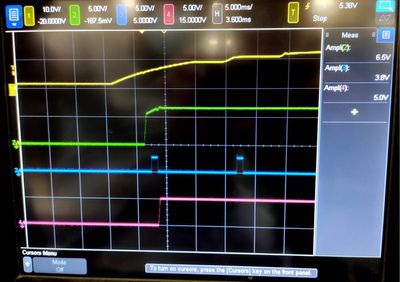

Please find the waveforms attached below of the start-up Sequence:

- Waveform 1:

- VSUP (Sluggish behavior is due to Power supply)

- VPRE

- Select Line

- VCORE

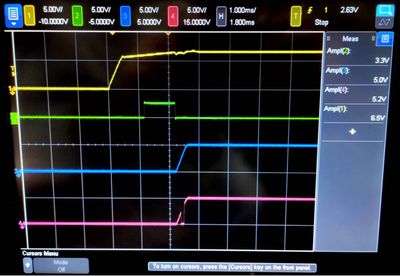

- Waveform 2:

- VPRE

- Select Pin

- VCORE

- Interrupt line

Kindly let me know what is causing the initial undervoltage and LBIST error ?

Regards,

Jasper Raj Immanuel

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jasper,

1. What's the voltage level of IO2,IO3 when device powerup ?

2. When IO2 voltage is 12V during device powerup,fail safe machine will stop and device will enter test mode, ABIST1 will fail. after IO2 go down, fail safe state machine will continue and ABIST1 will pass.

3. so our datasheet says max rating of IO2/IO3 is 8V, please make sure IO2/IO3 voltage are below 8V during powerup.

4. If LBIST fail during device powerup, it will not stop RSTB release and MCU can send SPI command to SBC, but FS0B/FS1B will not be released due to LBIST fail.

Brs

Allan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello @allan

Customer has provided below feedback and follow up query :

Kindly find below the update and further query wrt to our application:

- LBIST Failure: as mentioned in the mail below.

- We went into isolating each part of the SBC to check which peripheral could be causing the issue.

- On isolating the IO-2 and IO-3 pin, the LBIST failure seems to be cleared.

- In our application, the IO-2 and IO-3 Pins are default pulled High. On studying the datasheet it was observed that the IO_23_FS bit of the INIT_FSSM register is default set to safety critical.

- The Suspect would be; that since the Pins are being pulled high (Default), the LBIST is being triggered and hence being treated as a failure.

Future Steps:

- Would our analysis (as mentioned above) hold true wrt to the LBIST being set?

- If this is the case, the LBIST failure would occur, during every Power on Reset and hence the module would fail.

- The idea for the work-around: the LBIST Failure during the first power on cycle would be ignored and during initialization the IO_23_FS bit would be configured as “0” i.e. NOT SAFETY and hence configuring IO2 and IO3 as wake-up inputs as required by our application.

- After initialization, The normal mode would be entered (after good WD refresh)

- Query: Would the IO_23_FS bit hold its value after wake-up from LPOFF mode and LBIST would not be triggered? (system sleep mode is where is cut off the 5V supply).

- Query: With the LBIST fault being set, is it possible to pass the Fail safe state machine to normal mode after good WD Refresh?

Kindly provide your feedback,

Regards,

Jasper

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Jasper,

1. What's the voltage level of IO2,IO3 when device powerup ?

2. When IO2 voltage is 12V during device powerup,fail safe machine will stop and device will enter test mode, ABIST1 will fail. after IO2 go down, fail safe state machine will continue and ABIST1 will pass.

3. so our datasheet says max rating of IO2/IO3 is 8V, please make sure IO2/IO3 voltage are below 8V during powerup.

4. If LBIST fail during device powerup, it will not stop RSTB release and MCU can send SPI command to SBC, but FS0B/FS1B will not be released due to LBIST fail.

Brs

Allan