- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

Connecting P2020 to P2020 over eTSEC

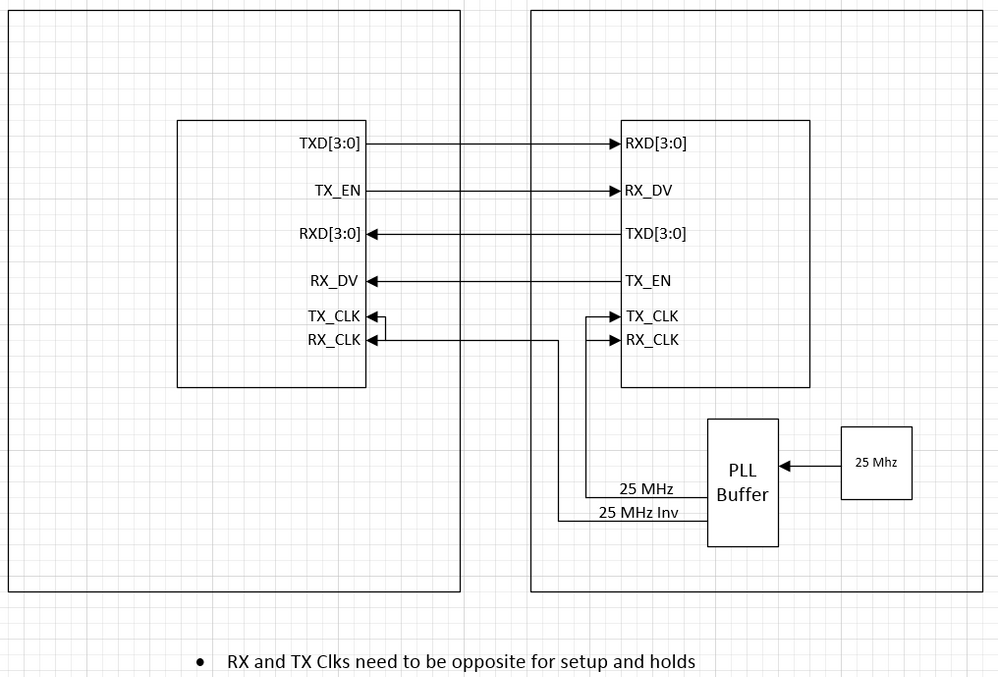

I am looking to connect two P2020 processors together over their eTSEC connections. My main limitation is that I need to keep all signals below 40Mhz. As far as I can tell, my best bet is to use the MII interface at 2.5 or 25 MHz. Can I just hook it up like this:

I would then tie the collision, carrier_sense, and rcv_error signals in the proper state to allow communication.

Is there anything wrong with this plan?

Thanks,

Todd

Have a great day,

Yes you can connect the P2020 in this way. Care must be taking in the setup and hold timings on the two MAC devices. See as example timing analysis in ZARLINK app note “Ethernet Switch MAC-to-MAC Connections”.

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Serguei,

Thank you for the confirmation and the timing warning. I have been looking at the output delay, setup, and hold times, and the timing seems tricky for 100mbps operation. For a 25Mhz clock, the period would be 40ns, the TX_CLK to data delay is 1-15ns, and setup and hold times are 10 ns. If one TX_CLK to data delay is 15ns and then the following one is 1ns, there is only 26ns of valid data there. To allow for 10ns setup and hold times, the RX_CLK edge would seem to have to be pretty precise! Am I looking at something incorrectly, or is there any more accurate timing on the TX_CLK delay that could help?

Thanks,

Todd