- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

Hi.

Our system uses SJA1105QEL ethernet switch (Host is MPC5748G).

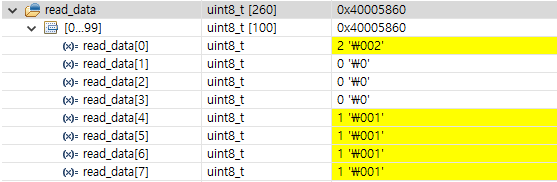

I want to read configuration value. so i tried to access address 0x00000000 (ETH_DYN 0x00h) but the result of read access is same as write access (SDO is mirrored as SDI).

According to the software manual, i understand that first 32 bits are access control value and next 32 bits are ignored value for reading data.

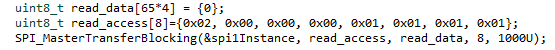

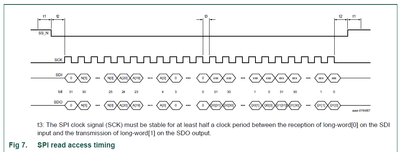

So, i tested following method in S32 project.

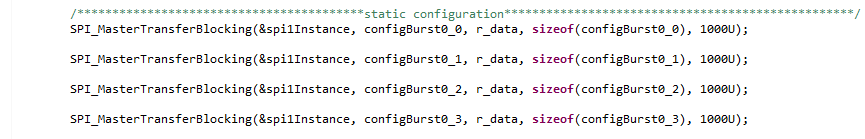

-test code

-result

Do you think this method is wrong or other problem exists?

please any help for me.

best regards.

thank you.

已解决! 转到解答。

Data (containing the number of 32-bit quadlets to be read and address to read from) is

received on the SDI input of the switch and is treated as a sequence of 32-bit quadlets.

Data corresponding to the address received is output on SDO pin of the switch.

Dear guoweisun.

thank you for your reply.

In my case, i want to read a register value at 0x00.

Where read access, i understand first 32 bits are mirrored same data via SDO.

I expect to read next not mirrored 32 bits data via SDO. but the next 32 bits are also mirrored SDI data.

i think it is something wrong.

is my test code wrong or not?

best regards.