- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear NXP Colleagues:

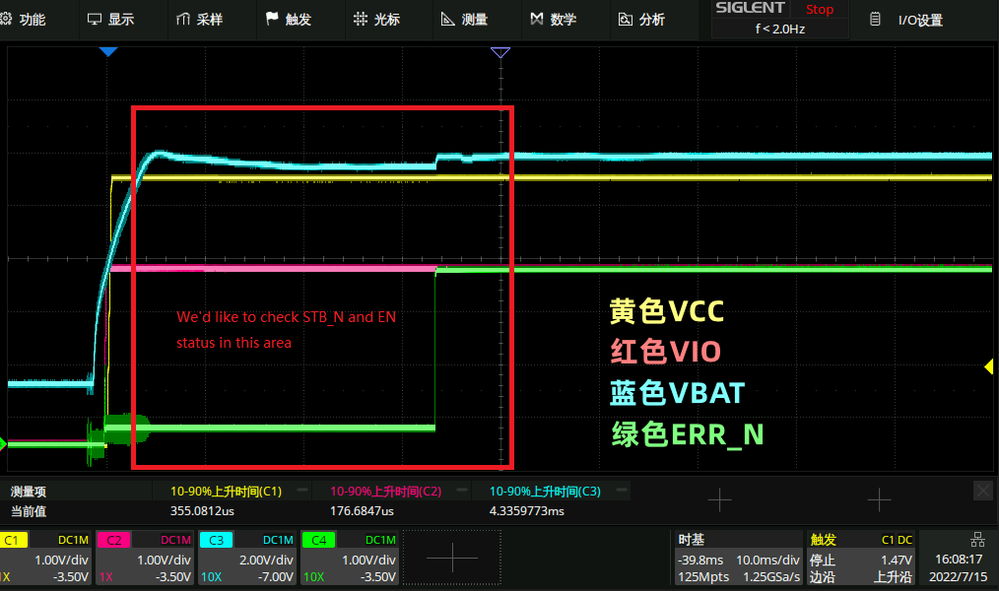

We use TJA1043 as CAN Transceiver. We found an abnormal voltage on the ERR_N pin during the cold start stage. ERR_N pin cannot be pulled high for 35.5ms. You can get more information from the attached picture. We want to know how ERR_N works and its internal block diagram.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Yang,

This spike happens at the beginning stage of Vio rising to the working voltage, which means MCU initialization is not finished already and would not have reliability issues.

Best regards,

Tomas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi NXP team,

I have tried to create the new ticket but i couldn't not.

So i just posting my queries here as the queries belongs to TJA1043 ERR_N pin monitoring.

1. ERR_N pin state is getting change during Bus off (CANH to GND/CANL to VBAT)

When CANH to GND, ERR_N pin is toggling

When CANL to VBAT, ERR_N pin is low

Because of the ERR_N pin state got changed during Bus off, we are setting the fault for both Bus off and ERR_N monitoring. can you please please confirm whether this is the expected behavior?

2.When we make CANH to VBAT or CANL to GND, CAN communication should be happen or not?

Because some times CAN communication is happening and sometimes is not happening

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Tomas,

I have already read Section 7.1&7.2 of the datasheet and Section 6.5 of the attached AH1014. These Sections only describe the state of the ERR_N pin after power-on. But We want to know how ERR_N works at the beginning of power up.

Best regards,

Yang

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Yang,

TJA1043 ERR_N is not only relevant to power supply, but also relevant to its operation mode. Could you please also provide STB_N and EN in waveform when both VCC/VIO is ready?

Best regards,

Tomas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

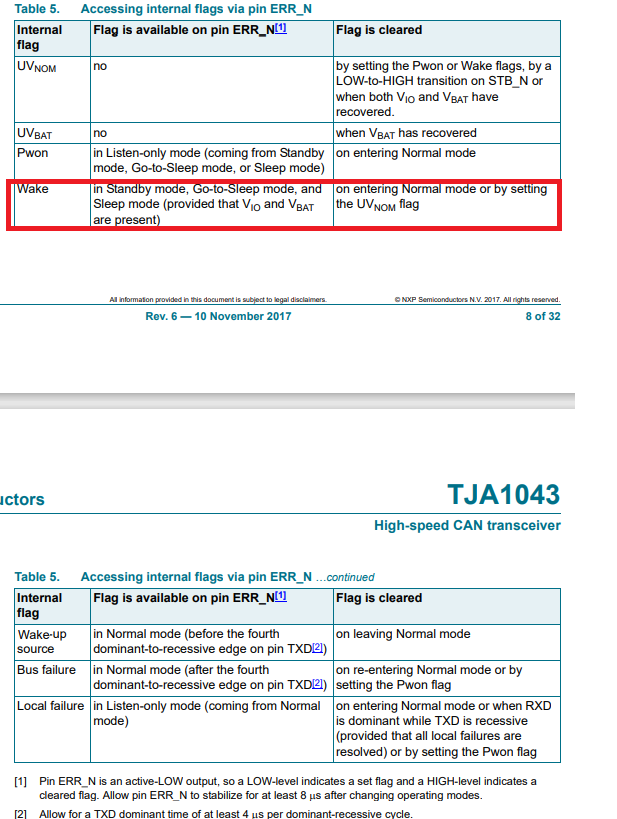

Dear Yang,

For the detailed description of ERR_N pin, please refer to the table below.

According to the signals, the TJA1043 should be in Standby mode, please check Wake flag.

Best regards,

Tomas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

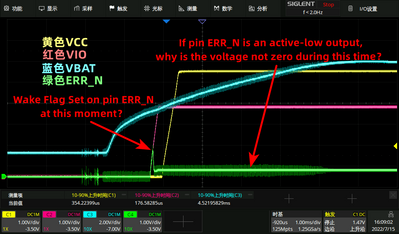

Dear Tomas,

I still have some doubts about the voltage on ERR_N pin. I know Pin ERR_N is an active-low output,when wake flag is availabe. But We observe a 300mV voltage on the pin,how to explain?

Best regards,

Yang

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

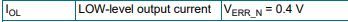

Dear Yang,

This voltage spike is the undetermined state of the MCU IO pins when Vio is powered. It should disappear if ERRN is disconnected from MCU.

And the question in the figure “if pin ERR_N is an active-low output, why is the voltage not zero during this time?”

Answer: VERR_N is 0.4V when it is at a low level.

Best regards,

Tomas

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Tomas,

"This voltage spike is the undetermined state of the MCU IO pins when Vio is powered."

---Will this voltage spikes cause TJA1043 reliability failures?

Best regards,

Yang

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Dear Yang,

This spike happens at the beginning stage of Vio rising to the working voltage, which means MCU initialization is not finished already and would not have reliability issues.

Best regards,

Tomas