- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- Product Forums

- :

- Other NXP Products

- :

- PN7462 Memory Allocation Problem

PN7462 Memory Allocation Problem

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

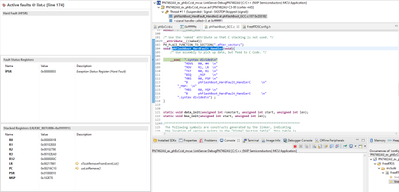

Hi,

I'm using PN7462AU_ex_phExCcid sample from 'PN7462AU FW and SW Examples Full Version - v06.10.00' with 'OM27462CDKP: NFC Controller development kit'.

I'm trying to add an array like this 'uint8_t tempBuffer[600]' as a global variable in 'phExCcid.c' file.

Than just for testing purposes i change item of an array like this 'tempBuffer[400] = 0x2' in 'int main(void)' in 'phExCcid.c' file.

OR

I tried to access that array from one of RTOS task.

After these changes sometimes firmware ends up in "phFlashBoot_HardFault_Handler" sometimes it just freezes.

If I try to increase stack sizes of RTOS tasks i'm getting "vApplicationMallocFailedHook".

I tried to change "Heap & Stack placement" and their sizes in MCU Linker-> Managed Linker Script settings but i didn't get any result.

I've been dealing with this problem for days without any result. I already read datasheet and documents given with the product. I think the change that needs to be made is quite simple, but I couldn't find it.

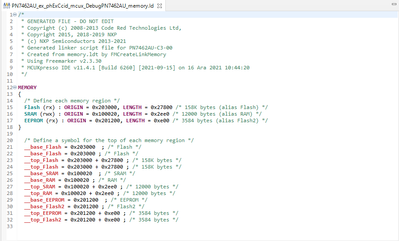

/*

* GENERATED FILE - DO NOT EDIT

* Copyright (c) 2008-2013 Code Red Technologies Ltd,

* Copyright 2015, 2018-2019 NXP

* (c) NXP Semiconductors 2013-2021

* Generated linker script file for PN7462AU-C3-00

* Created from linkscript.ldt by FMCreateLinkLibraries

* Using Freemarker v2.3.30

* MCUXpresso IDE v11.4.1 [Build 6260] [2021-09-15] on 16 Ara 2021 10:44:20

*/

INCLUDE "PN7462AU_ex_phExCcid_mcux_DebugPN7462AU_library.ld"

INCLUDE "PN7462AU_ex_phExCcid_mcux_DebugPN7462AU_memory.ld"

ENTRY(ResetISR)

SECTIONS

{

.text_Flash2 : ALIGN(4)

{

FILL(0xff)

*(.text_Flash2) /* for compatibility with previous releases */

*(.text_EEPROM) /* for compatibility with previous releases */

*(.text.$Flash2)

*(.text.$EEPROM)

*(.text_Flash2.*) /* for compatibility with previous releases */

*(.text_EEPROM.*) /* for compatibility with previous releases */

*(.text.$Flash2.*)

*(.text.$EEPROM.*)

*(.rodata.$Flash2)

*(.rodata.$EEPROM)

*(.rodata.$Flash2.*)

*(.rodata.$EEPROM.*) } > EEPROM

/* MAIN TEXT SECTION */

.text : ALIGN(4)

{

FILL(0xff)

__vectors_start__ = ABSOLUTE(.) ;

KEEP(*(.isr_vector))

/* Global Section Table */

. = ALIGN(4) ;

__section_table_start = .;

__data_section_table = .;

LONG(LOADADDR(.data));

LONG( ADDR(.data));

LONG( SIZEOF(.data));

__data_section_table_end = .;

__bss_section_table = .;

LONG( ADDR(.bss));

LONG( SIZEOF(.bss));

__bss_section_table_end = .;

__section_table_end = . ;

/* End of Global Section Table */

*(.after_vectors*)

} > Flash

.text : ALIGN(4)

{

*(.text*)

*(.rodata .rodata.* .constdata .constdata.*)

. = ALIGN(4);

} > Flash

/*

* for exception handling/unwind - some Newlib functions (in common

* with C++ and STDC++) use this.

*/

.ARM.extab : ALIGN(4)

{

*(.ARM.extab* .gnu.linkonce.armextab.*)

} > Flash

.ARM.exidx : ALIGN(4)

{

__exidx_start = .;

*(.ARM.exidx* .gnu.linkonce.armexidx.*)

__exidx_end = .;

} > Flash

_etext = .;

/* MAIN DATA SECTION */

.uninit_RESERVED (NOLOAD) : ALIGN(4)

{

_start_uninit_RESERVED = .;

KEEP(*(.bss.$RESERVED*))

. = ALIGN(4) ;

_end_uninit_RESERVED = .;

} > SRAM AT> SRAM

/* Main DATA section (SRAM) */

.data : ALIGN(4)

{

FILL(0xff)

_data = . ;

PROVIDE(__start_data_RAM = .) ;

PROVIDE(__start_data_SRAM = .) ;

*(vtable)

*(.ramfunc*)

KEEP(*(CodeQuickAccess))

KEEP(*(DataQuickAccess))

*(RamFunction)

*(.data*)

. = ALIGN(4) ;

_edata = . ;

PROVIDE(__end_data_RAM = .) ;

PROVIDE(__end_data_SRAM = .) ;

} > SRAM AT>Flash

/* MAIN BSS SECTION */

.bss : ALIGN(4)

{

_bss = .;

PROVIDE(__start_bss_RAM = .) ;

PROVIDE(__start_bss_SRAM = .) ;

*(.bss*)

*(COMMON)

. = ALIGN(4) ;

_ebss = .;

PROVIDE(__end_bss_RAM = .) ;

PROVIDE(__end_bss_SRAM = .) ;

PROVIDE(end = .);

} > SRAM AT> SRAM

/* DEFAULT NOINIT SECTION */

.noinit (NOLOAD): ALIGN(4)

{

_noinit = .;

PROVIDE(__start_noinit_RAM = .) ;

PROVIDE(__start_noinit_SRAM = .) ;

*(.noinit*)

. = ALIGN(4) ;

_end_noinit = .;

PROVIDE(__end_noinit_RAM = .) ;

PROVIDE(__end_noinit_SRAM = .) ;

} > SRAM AT> SRAM

PROVIDE(_pvHeapStart = DEFINED(__user_heap_base) ? __user_heap_base : .);

PROVIDE(_vStackTop = DEFINED(__user_stack_top) ? __user_stack_top : __top_SRAM - 1528);

/* Provide basic symbols giving location and size of main text

* block, including initial values of RW data sections. Note that

* these will need extending to give a complete picture with

* complex images (e.g multiple Flash banks).

*/

_image_start = LOADADDR(.text);

_image_end = LOADADDR(.data) + SIZEOF(.data);

_image_size = _image_end - _image_start;

}

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @EE_Ark

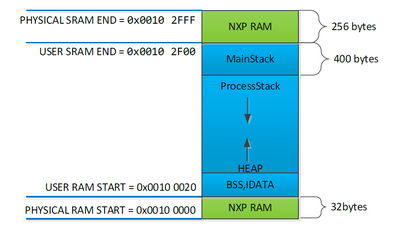

Please be aware that for PN7462 , the user SRAM is limited to 12000 bytes and 256 bytes is used by NXP FW executed in ROM. Heap , stack and BSS and some reserved RAM need to be stored in this area. see below picture.

if you add an array like this 'uint8_t tempBuffer[600]' as a global variable in 'phExCcid.c' file. this will add more 738 bytes (I tested on my side) in BSS. it means the size of heap and stack will be reduced by 738 bytes. why do you need so large array in this memory constrained device?

If the size of heap and stack reduced by 738 bytes, there there will be a conflict issue of heap and stack. will result in system crash.

You can try to build the release version, it can work without issues if you add the large array.

To avoid the conflict, one option you can try is to reduce the stack size of other tasks.

For example , I reduced the clif task size by 100 bytes, there will be no errors on my side, You need to do more test .

change the cli stack size in phExCcid_Cfg.h

line 62

from

#define PH_EXCCID_CFG_RTOS_CLIF_TASK_STACK_SIZE (440 + PH_EXCCID_CFG_RTOS_STACK_GUARD + PH_EXCCID_CFG_CLIF_LOG_STACK)

to

#define PH_EXCCID_CFG_RTOS_CLIF_TASK_STACK_SIZE (340 + PH_EXCCID_CFG_RTOS_STACK_GUARD + PH_EXCCID_CFG_CLIF_LOG_STACK)

I hope it helps

Regards

Daniel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @EE_Ark

Please be aware that for PN7462 , the user SRAM is limited to 12000 bytes and 256 bytes is used by NXP FW executed in ROM. Heap , stack and BSS and some reserved RAM need to be stored in this area. see below picture.

if you add an array like this 'uint8_t tempBuffer[600]' as a global variable in 'phExCcid.c' file. this will add more 738 bytes (I tested on my side) in BSS. it means the size of heap and stack will be reduced by 738 bytes. why do you need so large array in this memory constrained device?

If the size of heap and stack reduced by 738 bytes, there there will be a conflict issue of heap and stack. will result in system crash.

You can try to build the release version, it can work without issues if you add the large array.

To avoid the conflict, one option you can try is to reduce the stack size of other tasks.

For example , I reduced the clif task size by 100 bytes, there will be no errors on my side, You need to do more test .

change the cli stack size in phExCcid_Cfg.h

line 62

from

#define PH_EXCCID_CFG_RTOS_CLIF_TASK_STACK_SIZE (440 + PH_EXCCID_CFG_RTOS_STACK_GUARD + PH_EXCCID_CFG_CLIF_LOG_STACK)

to

#define PH_EXCCID_CFG_RTOS_CLIF_TASK_STACK_SIZE (340 + PH_EXCCID_CFG_RTOS_STACK_GUARD + PH_EXCCID_CFG_CLIF_LOG_STACK)

I hope it helps

Regards

Daniel