- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

NTAG NT3H2111 Connecting problem

Hi,

I have connected an NTAG antenna (with NT3H2111 implemented on it) to an existing I2C bus of an FPGA.

I followed the read/write register sequence appeared on the datasheet but I don't get any response from the NT3H. From looking at the SDA bus - I get no ACK from the NT3H. When I try to write to a session\configuration register - While writing i can see on the NXP mobile app that the NTAG memory is locked, but after the write sequence ends: I cant see any change on the registers.

The SCL bus frequency is 100KHz and the NTAG is connected to GND, VCC, SDA and SCL.

What can be the problem?

Thnaks, Matan

Hello Matan,

- Have you confirmed that the slave address is correct?

By default the slave address is 0x55.

- What register address are you trying to read or write?

You mentioned an NFC mobile app. If the phone has taken control and arbitration is locked to the NFC side (RF_LOCKED = 1) then the NT3H2111 will not respond to any command from the I2C side other than the READ register command.

- The READ/WRITE register sequence is only for SESSION registers. For CONFIGURATION registers, SRAM or EEPROM you need to use the normal READ/WRITE operation.

- After power on it is recommended to wait for 500 us before sending commands to the IC.

Hope this helps!

Best Regards!,

Jorge Gonzalez

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Jorge, thank you for your answer!

I managed to read\write session registers, apparently (after scope check on the explorer kit ) there is a short delay between each transferred byte.

Unfortunately, I can't read nor write to the configuration registers (as well as the SRAM which you mentioned work the same).

I think i have some problem with the timing:

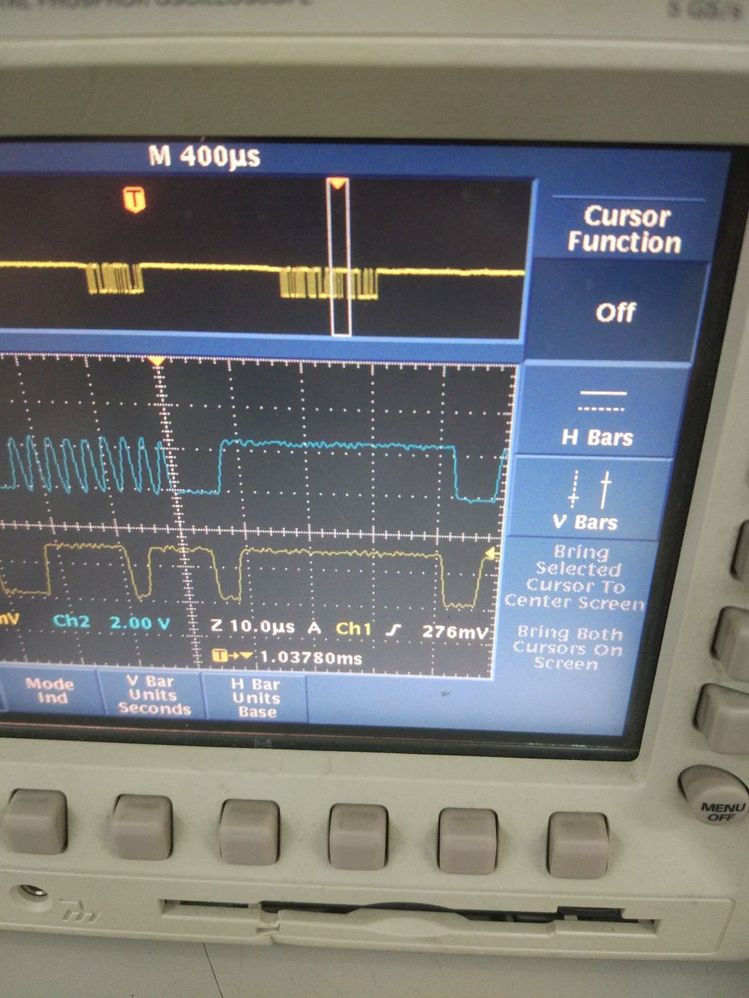

The picture at the bottom was taken from the explorer kit and describing "Read" action. The datasheet says to have at least 50us between "stop" and "start" conditions - but here there are only 30us.

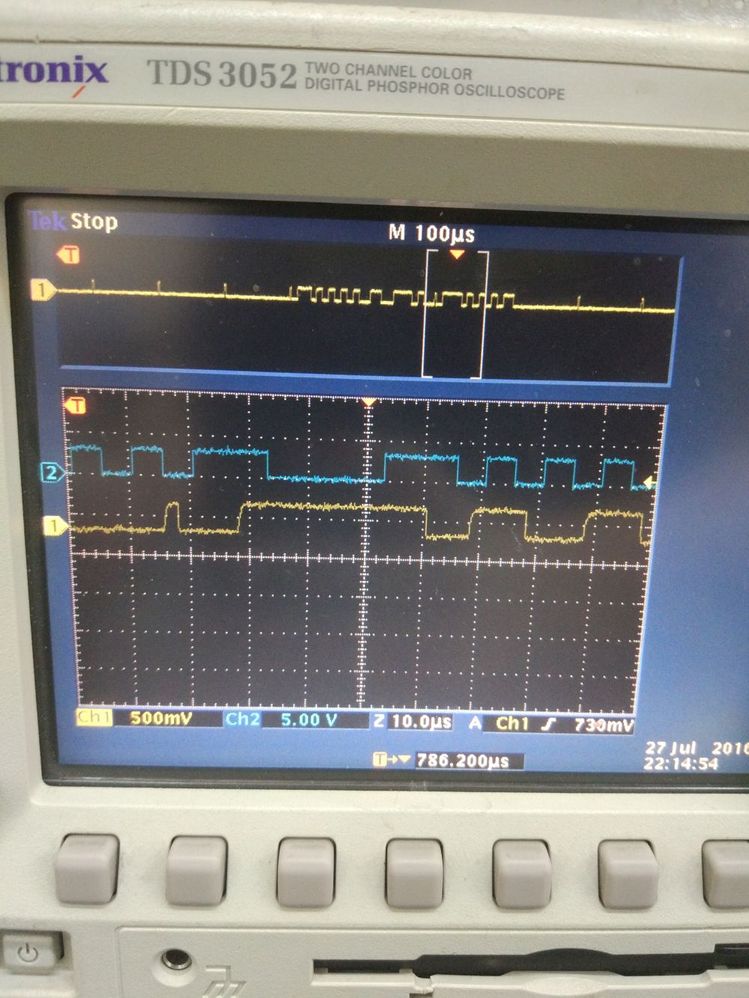

The next picture is my implementation one. Even though i maintained almost identical gap between "stop" and "start" - i still get no data out of the NTAG.

Any idea what could have happened? Thanks

Hi Matan,

The 50 us delay is only required if clock stretching is disabled, but by default it is enabled.

Do you have some full frames of the scope to share?

From your picture I cannot infer what is wrong.

Hi Jorge,

Thanks again for your help. I managed to overcome some errors (apparently my NTAG address is 4Ch) and now I can read and write data and registers for the NTAG.

On the next step I want to implement is the ability to write & read small files using pass-through mode, for doing that I have a few questions:

- Activating pass-through mode: I've changed NC_REG (Config.) to 41h in order to turn ON PTHRU_ON_OFF bit. However, the session register doesn't update and I don't know if pass-through is valid or not. Iv'e seen POR is required - how can I do Pwer On Reset?

- Whenever I'm performing Write to the NTAG via I2C and in the same time trying to access the NTAG with the mobile app - it says to NTAG is locked and none of the passwords (SUN, MOON...) works to unlock it. Since my final goal is to transfer a file greater than 64Kb: I will need the ability to read the data from the NTAG's SRAM with the mobile app as soon as it appears there, so I'll be able to collect it (kinda like RS232 Tx/Rx way of work). Can it be done?

Thanks again,

Matan