- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- MQXソフトウェアソリューション

- :

- MQXソフトウェアソリューション

- :

- Re: Hi,I try to start MQX 4.1.1 on FRDM64F platform with IRC48M.

Hi,I try to start MQX 4.1.1 on FRDM64F platform with IRC48M.

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

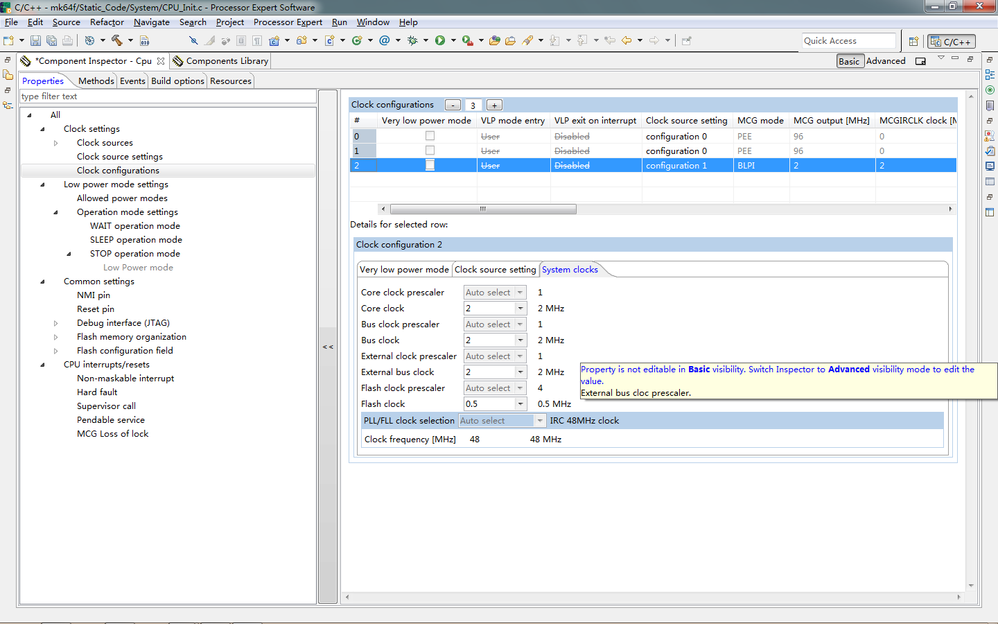

Hi,I try to start MQX 4.1.1 on FRDM64F platform with IRC48M. According to the AN4905 documentation,do the relevant configuration. but each time OS is stopped in PBE mode, wait until external reference clock is selected as MCG output. I am very upset, please expert help, thank you!

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

配置MCG为BLPE模式,主频48MHZ,配置成功!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

hope the freescale official providing the demo for K64 without external crystals on the crystal-less USB operation.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi qingjun wang,

This issue is caused if the board has a different clock configuration. If customer has a different configuration he needs to change the BSP. Attached to this mail, you can find a document that explains how to change the default clock configurations.

Please let me know if this helps!!

Have a great day,

Sol

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi soledad!

Faced with my problem, can you help me?

Thank you.

Qingjun Wang

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi soledad! Thank you for you help!

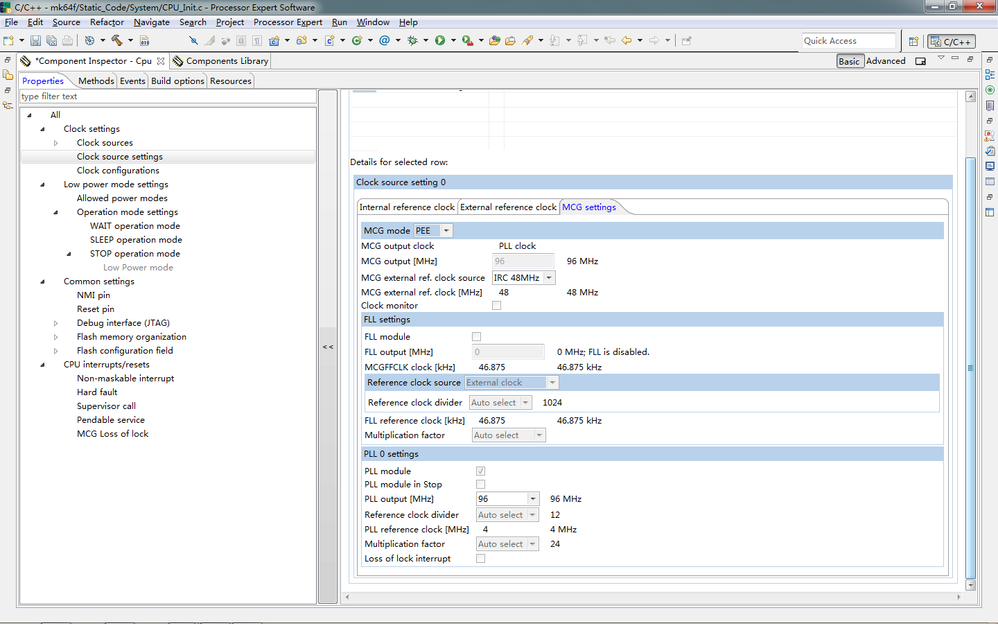

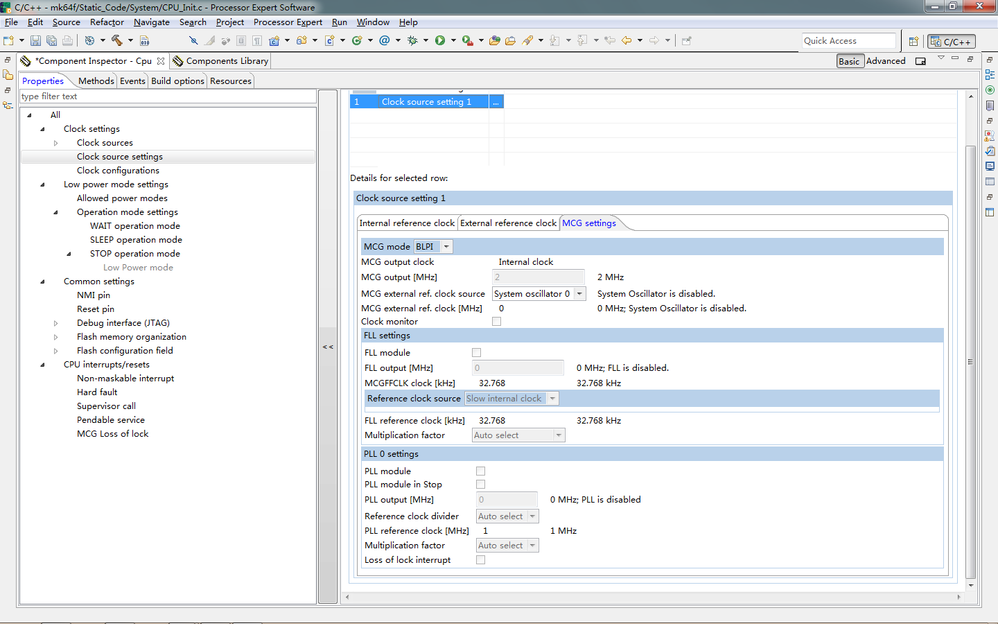

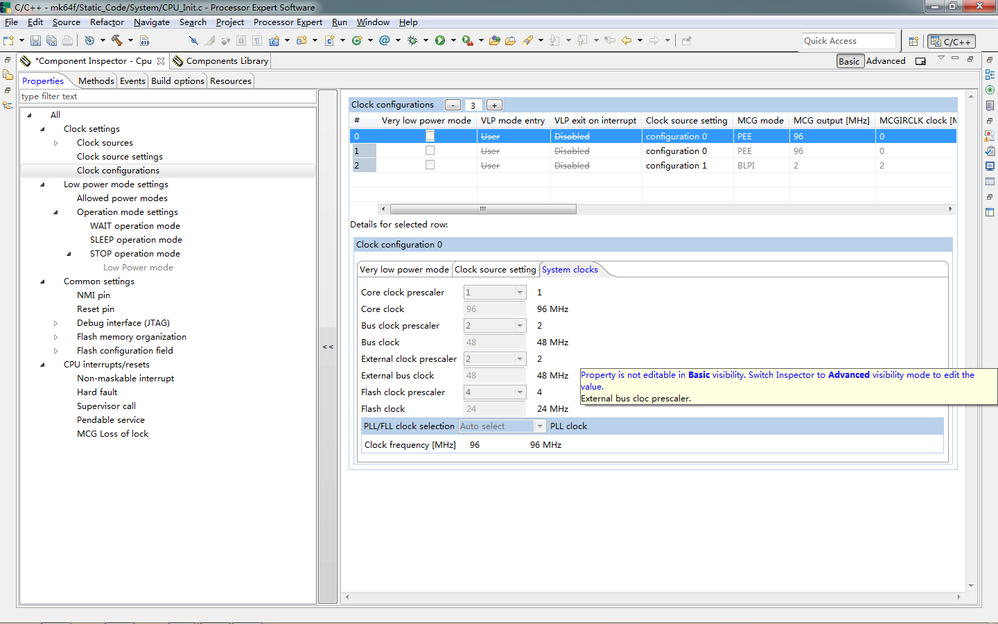

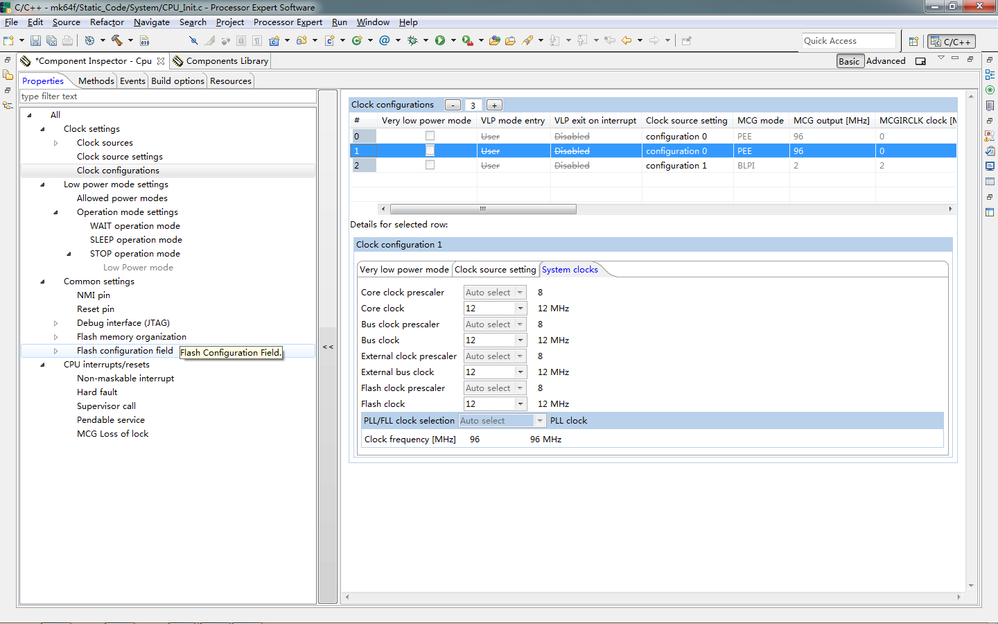

According to your document, I use PE to do the configuration, But still not solve the problem.

PE configuration as follows:

Add the following content in the _bsp_initialize_hardware(void) functions:

/* SIM_CLKDIV2:USBDIV = 0, USBFRAC = 0*/

SIM_CLKDIV2 = (uint32_t)0x0UL;

/* Configure USB to be clocked from IRC 48MHZ */

SIM_SOPT2_REG(SIM_BASE_PTR) |= SIM_SOPT2_USBSRC_MASK | SIM_SOPT2_PLLFLLSEL(3);

/*Enable USB-OTG IP clocking */

SIM_SCGC4_REG(SIM_BASE_PTR) |= SIM_SCGC4_USBOTG_MASK;

/* Enable IRC48MHZ for USB module*/

USB0_CLK_RECOVER_IRC_EN = 0x03;

/* MCG_C7: OSCSEL = 10*/

MCG_C7 |= 0x2u;

/* USB_CLK_RECOVER_CTRL: CLOCK_RECOVER_EN = 1*/

USB0_CLK_RECOVER_CTRL |= ( 1UL << 7);

The problem is OS stay on the PBE patterns, wait until external reference clock is selected as MCG output or wait until PLL is locked.

Thank you for your selfless help again!