- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

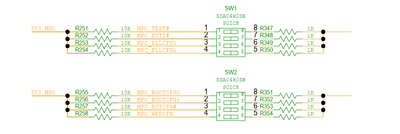

您好, 我有个新的问题。 我想问下电路板这些引脚怎么设置才能用调试器从jtag口下载调试呢?

Hello, I have a new question. I would like to ask how to set these pins of the circuit board to download debugging from the jtag port with the debugger?

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

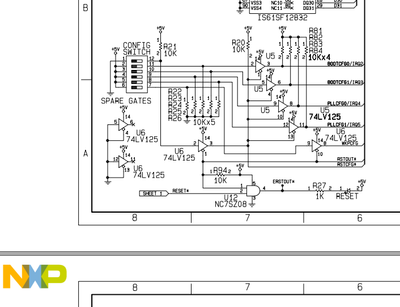

If you have

CONFIG enable = OFF, i.e. rest is ignored and default, internal, crystal reference is used

equivalent configuration is

CONFIG enable = ON, i.e. RSTCFG = config from pins below

BOOTCFG1=OFF,

BOOTCFG2=OFF, i.e. internal

PLLCFG0=ON,

PLLCFG1=OFF and i.e. crystal reference

WKPCFG = ON,

BOOTCFG/PLLCFG description you may find in the device's RM.

Anyway PLLCFG configuration needs to fit used HW setup, BOOTCFG should not matter in the context of debugger connection and downloading SW unless device is censored.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

If you have

CONFIG enable = OFF, i.e. rest is ignored and default, internal, crystal reference is used

equivalent configuration is

CONFIG enable = ON, i.e. RSTCFG = config from pins below

BOOTCFG1=OFF,

BOOTCFG2=OFF, i.e. internal

PLLCFG0=ON,

PLLCFG1=OFF and i.e. crystal reference

WKPCFG = ON,

BOOTCFG/PLLCFG description you may find in the device's RM.

Anyway PLLCFG configuration needs to fit used HW setup, BOOTCFG should not matter in the context of debugger connection and downloading SW unless device is censored.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

还有 EVTI#需要怎么配置呢

And how to configure EVTI#

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

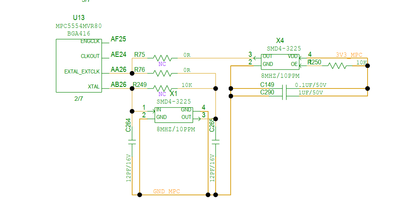

好的非常感谢您的回答,请问我们这个硬件需要怎么配pll呢?

Ok, thank you very much for your answer. May I ask how we need pll for this hardware?