- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- MPC5777C injection ecc ram error

MPC5777C injection ecc ram error

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

MPC5777C injection ecc ram error

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi all

I would like introduce a unit test to check if ERM is able to get PRAMAC_0 uncorrectable errors.

I m using the EIM module but I found this kind of problem:

a) EIM is not able to inject a error only on one specific read access, so after having set EIM.EICHEN.R= 0x80000000

and EIM,EIMCR.R=1 i think all access on RAM managed by PRAMAC_0 is "wrong".

b) The result of a) , from point of view of my set-up, is that also into IVOR exeception somethings is wrong and system will go into IVOR13 LOOP call (we are using MMU and we are working at lauterbach)

I also tried to remove EIM.EIMCR.R enable with this :

.align 4

.globl EXCP_Iv12_Hnd

EXCP_Iv12_Hnd:

e_b exception_IVOR_12

.align 4

.globl EXCP_Iv13_Hnd

EXCP_Iv13_Hnd:

e_bl EIMCR_Reset

e_b exception_IVOR_13

.align 4

.globl EXCP_Iv14_Hnd

EXCP_Iv14_Hnd:

e_b exception_IVOR_14

.align 4

.globl EXCP_Iv15_Hnd

EXCP_Iv15_Hnd:

e_b exception_IVOR_15

I know that is not a real case! But I would like to have a test set-up where observe and trace what can do in a "possibile" fault reaction

I think that EIM has introduced a general error on MMU managememt. How is it possibile insert Uncorrectable Errors into RAM but only into single location?

I would like found a "similar" test condition how can be realized for testing ECC EDC flash using UTEST area!

Is possible?

Do you have a suggest?

Regards and thanks to all!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, that's just disadvantage of EIM module. It simply inverts specified data/checksum line on the internal data bus, but for all accesses upon injection enabling. It means the code must disable error injection before next access to area specified by EIM channel.

As double bit ECC error leads in machine check exception, its handler must disable error injection at the very beginning and the handler itself must be stored in different memory than the one where ECC error is injected into. It means in case ECC error is injected to the SRAM, exception handler needs to be located in FLASH or be locked in CACHE.

UTEST area may used for simulating of ECC/EDC error in FLASH.

On this device, for all internal RAM error injection, EIM module needs to be used.

Example code you may find here:

Example MPC5777C-1b+2b_RAM_ECC_error_injection GHS614

For FLASH, you may also use flash over-programming:

Example MPC5777C-1b+2b_FLASH_ECC_error_injection GHS614

ECC with using of UTEST I have preprared only for MPC5744P device (having MEMU instead of ERM):

https://community.nxp.com/docs/DOC-339955

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

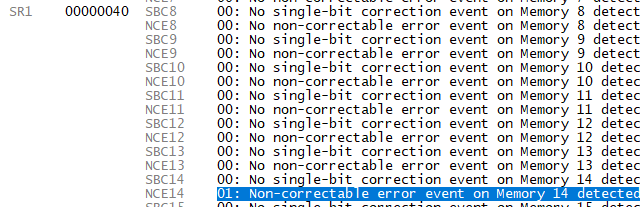

I have a question regarding this topic. I am able to generate the fault in the ERM by reading the UTEST area.

I also have the following init:

// Enable EDC after ECC Error Detection

C55FMC.UT0.B.CPE = 1;

area *utest_ecc_flash = (uint32*)0x00400060;

But I cannot see the FAULT being propagated to the FCCU.

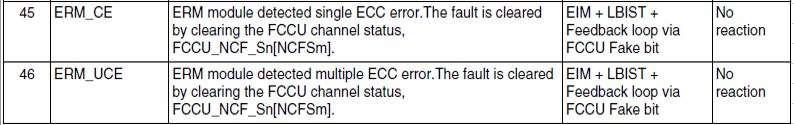

I would expect to see the FCCU status [45] [46].

Is this correct:

Do you have any suggestion?

Thanks

Federico

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It is needed to have these faults enabled in the FCCU.

Pay attention to following appnote to understand how to handle FCCU:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi David. Thanks for your confirmation about this question.

I had already analyzed your ANxx document. I must say it was very useful to understand the particularities of the MPC5777C compared to other MPC5xx processors. I also already used your sample code as inspiration to implement some testing path.

Many Thanks.