- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

[MPC5777C] How can i cause exception error or unidentified interrupt?

Hi, Dear

Our development environment here

MCU : MPC5777C

OS : ETAS RTA OS

Compiler : Windriver diab 5.9.4

I want to exception handler test, so I have to make some kind of exception error.

Refer to e200z760RM(315page), MPC5777C has Machine check(IVOR1) and Program(IVOR6).

I don't know that what i have to do for causing a exception error.

In specific, I want to test "Illegal instruction exception", "Data cache parity error" and Exception handler which is cased by specified error.

In other words, I want to fault injection method above them.

Please let me know what i have to do.

Thank you.

Hello Jongmin,

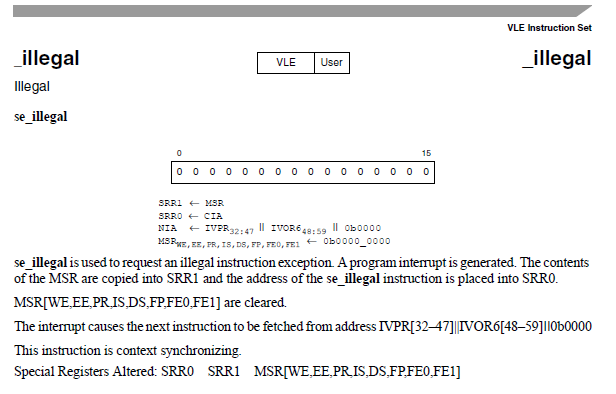

Have you tried the instruction se_illegal? that seems to be exactly what you need for the illegal instruction exception.

Other ideas may be:

- Try to write to a register of a peripheral that is not enabled.

- Try to write to an reserved/invalid memory address

For the parity error, I'm not sure if trying to read from a RAM location that has not been initialized (never written) would do the trick.

Thank you for your answer.

I have solved this question.

First of all, For the illigal insturction error, I try to execute instruction at the unused area.. Then exception error is arised.

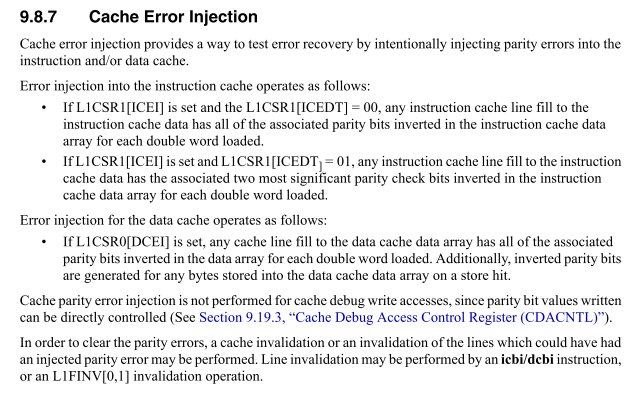

Cache parity error is arised by cache controller, cache error injection.

Is it right solution?

Hi,

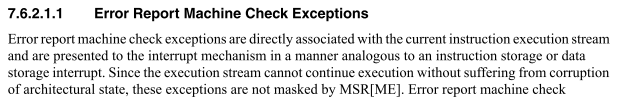

when you access memory (either instruction fetch or data load/store) and bus error occurs (unimplemented memory, ECC error...) then IVOR1 is triggered regardless of MSR[ME].

Read the chapter "7.6.2 Machine Check Interrupt (IVOR1)" in core reference manual for more details:

http://www.nxp.com/files/32bit/doc/ref_manual/e200z760RM.pdf

If a bus error does not occur during instruction fetch but invalid opcode is loaded (or se_illegal is used) then IVOR6 is triggered.

Yes, it is possible to inject the error to cache:

Cache errors will trigger IVOR1 exception. See the tables:

Table 7-10. Error Report Machine Check Exceptions

Table 7-11. Asynchronous Machine Check Exceptions

... in core reference manual.

Regards,

Lukas