- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

-

Hello,

I'm working on a new design where we use the MPC5674F EBI to connect an FPGA in 16-bit muxed data/addr mode (D_ADDR_16_31 routed to FPGA).

The FPGA behaves just like a SRAM from the cpu point of view, and we have an assembled prototype already.

Reading trough the datasheet, ref. manual or the External_Bus_Interface_FAQs_draftC.pdf documents didn't clarified this to me.

UserMan section "29.4.2.7 Size, Alignment and Packaging on Transfers" states:

• 16-bit access, address bit 31 must be 0, and

• The EBI never generates a misaligned external access

Our expectation is that we could map 64Kaddr (128Kbytes) on the FPGA, but our current tests show that we cannot access odd addresses on the EBI.

Is that a real limitation of this microcontroller or am I doing something wrong?

已解决! 转到解答。

Your schematic does not help me too much as I don’t see there how these lines are processes by FPGA. Expected usage of multiplexed addresss/data but is using of external address latch, what’s in your case is apparently managed by FPGA itself.

The example you have pointed out assumes standard memory connection as described in section 4 of mentioned document.

It means ADD31 is unconnected and its functionality is basically replaced by WE0 and WE1 lines, the same way I would expect FPGA would be connected to EBI module.

Your address mask is 0xFFFF8000 =

0b1111_1111_1111_1111_1000_0000_0000_0000

Final address will be

0b0011_0000_0000_0000_0xxx_xxxx_xxxx_xxxx

Number of xs there is 15 thus address range 2^15=32kByte

You have 16-bit port. It means ADD31 is not connected.

0b0011_0000_0000_0000_0XXX_XXXX_XXXX_XXXx

Let’s say you have 8-bit write on address 0x30000000

In address phase, all X address lines will be cleared and WE0 line will be asserted.

If you have 8-bit write on address 0x30000001

in address phase, all X address lines will be cleared and and WE1 line will be asserted.

Yes, but even if I change address mask to 0xFFFE0000, I can't address 128kBytes (64k 16-bit words), right? I'm limited to 64kBytes, because I can't use ADD31. Is there a way to configure a 16-bit data bus (even if it requires the EBI to be connected differently) to address by word, or is my only option to use a 32-bit data bus?

Hi, I don’t understand you too much. Yes, 29.4.2.7 says what you mentioned but it says following

„Natural alignment for the EBI means:

- Byte access can have any address

- 16-bit access, address bit 31 must be 0

- 32-bit access, address bits 30-31 must be 0

- For burst accesses of any size, address bits 29-31 must be 0”

and

“Even though misaligned non-burst transfers from internal masters are supported, the EBI naturally aligns the accesses when it sends them out to the external bus, splitting them into multiple aligned accesses if necessary.“

Yes, you can address the whole 128kByte range.

Could you show me your scheme of connection and your EBI setup? Also tell me details about the issue.

Hello,

I work on the same project as gabrielmarques, and I was assigned to this task.

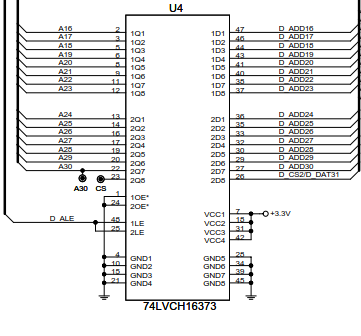

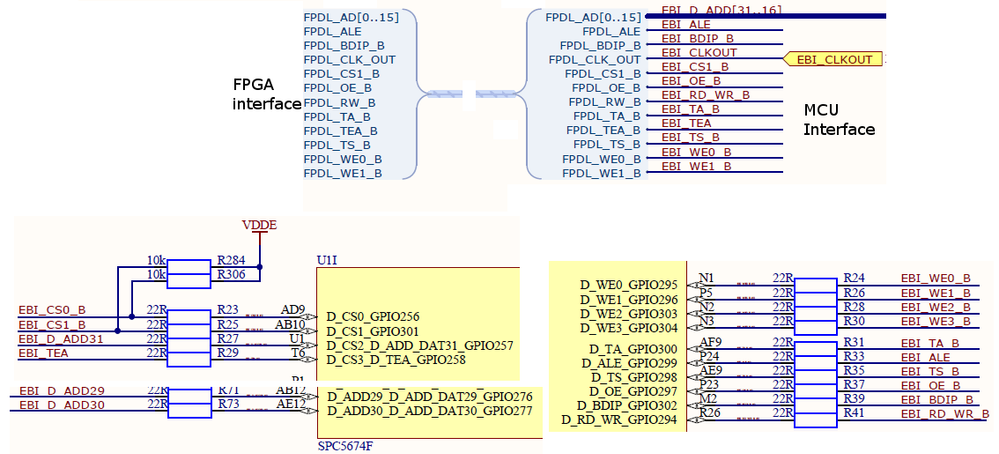

The following excerpts of our schematics show the EBI connections with the FPGA (Chip Select 1 is used with the FPGA):

The pins used are configured according to the following table:

| PCR No. | Pin Assignment | Function | Value |

|---|---|---|---|

| 256 | Primary | D_CS0 | 0x443 |

| 257 | Alternate 1 | D_ADD_DAT31 | 0x843 |

| 258 | Alternate 1 | D_TEA | 0x843 |

| 259-265 | Primary | D_ADD[12:15] | 0x443 |

| 263-277 | Alternate 1 | D_ADD_DAT[16:30] | 0x843 |

| 278-293 | Primary | D_ADD[16:30] | 0x443 |

| 294-304 | Primary | D_RD_RW, D_WE0, D_WE1, D_OE, D_TS, D_ALE, D_TA, D_CS1, D_BDIP, D_WE2, D_WE3 | 0x443 |

| 305-307 | Primary | D_ADD[9:11] | 0x443 |

EBI registers are configured with the following:

EBI_MCR = 0x804

EBI_CAL_BR1 = 0x300008A7

EBICALOR1 = 0xFFFF8000

On External_Bus_Interface_FAQs_draftC.pdf document, it is stated:

Internal address lines are assigned to external address lines the same way and in the same order. Considering you have set CS for whole EBI space in binary

0b001x_xxxx_xxxx_xxxx_ xxxx_xxxx_xxxx_xxxx_xxxx_xxxx

'x' here are mentioned bits 3-31

For instance, considering the device offers 22 address lines and non-multiplexed mode has been choosen, bits 9-30 will be reflected on the external bus D_ADD [9:30] ('X'):

0b001x_xxxx_xXXX_XXXX_XXXX_XXXX_XXXX_XXXx

There is 22 address line thus maximum memory size is 8Mbytes (=2^23 because of 16-bit data bus and so D_ADD31 is not used) per chip select.

This indicates that, on the above example, you can address 2^23 bytes, but only 2^22 addresses. On our example, using a 16-bit data bus, we can address 64Kbytes, but only 32K addresses. Is that correct?

Your schematic does not help me too much as I don’t see there how these lines are processes by FPGA. Expected usage of multiplexed addresss/data but is using of external address latch, what’s in your case is apparently managed by FPGA itself.

The example you have pointed out assumes standard memory connection as described in section 4 of mentioned document.

It means ADD31 is unconnected and its functionality is basically replaced by WE0 and WE1 lines, the same way I would expect FPGA would be connected to EBI module.

Your address mask is 0xFFFF8000 =

0b1111_1111_1111_1111_1000_0000_0000_0000

Final address will be

0b0011_0000_0000_0000_0xxx_xxxx_xxxx_xxxx

Number of xs there is 15 thus address range 2^15=32kByte

You have 16-bit port. It means ADD31 is not connected.

0b0011_0000_0000_0000_0XXX_XXXX_XXXX_XXXx

Let’s say you have 8-bit write on address 0x30000000

In address phase, all X address lines will be cleared and WE0 line will be asserted.

If you have 8-bit write on address 0x30000001

in address phase, all X address lines will be cleared and and WE1 line will be asserted.