- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- M_CAN MPC5777C registers format change between silicon / Reference Manual versions

M_CAN MPC5777C registers format change between silicon / Reference Manual versions

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

M_CAN MPC5777C registers format change between silicon / Reference Manual versions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am using MPC5777C processor.

I am writing an MCAN driver and I "discovered" that seem that registers (not only BTP, but also some others) are changed between silicon and reference manual revisions.

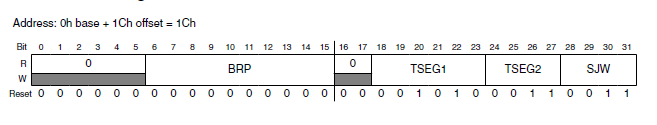

RM rev 4:

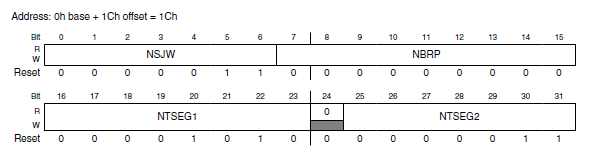

RM rev 8:

I discovered that also from documentation coming from core IP (M_CAN) developer the situation it is exactly the same (there is only a little tracking in release notes: "Register FBTP renamed to DBTP and restructured")

Shall I cope with both version of M_CAN (using M_CAN_CREL)? (I see someone have proposed a patch for this on linux kernel: can: m_can: fix bitrate setup on latest silicon - Patchwork )

I guess why in the last revision of manual there is nothing that let me know that exist a older version of M_CAN in old MPC5777C...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

By harvesting a little more I discovered exist two hardware maskset: 2N45H and 3N45H

And there is a pdf (MPC5777CRMAD.pdf) reporting (as a whole...) the older M_CAN peripheral chapter.

Are there others masksets?

What is the content of CREL register for both versions?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes, the MCAN was revised in the latest maskset and the latest RM (rev8) describes the functionality and programming model of maskset 3N45H.

With some exceptions, this RM also describes maskset 2N45H. For information about 2N45H's differences from 3N45H, see the MPC5777C Reference Manual Addendum (http://www.nxp.com/assets/documents/data/en/reference-manuals/MPC5777CRMAD.pdf).

BR, Petr

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you for the confirmation.

For us this is a problem due to software validation...

Is it possibile to know the possible values of M_CAN_CREL register expected on MPC5777C? In the RM is only reported an "example" of the value (and it is the same in RM and RM addendum).

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

below is CREL values for both masks...

2N45H: CREL = 0x30130506

3N45H: CREL = 0x32150320

The doc ticket will be raised to fix the RM.

BR, Petr