- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- Product Forums

- :

- MPC5xxx

- :

- Re: Help me with CAN_RXFGMASK MPC5746R

Help me with CAN_RXFGMASK MPC5746R

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Help me with CAN_RXFGMASK MPC5746R

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I've read the Reference Manual description of the CAN_RXFGMASK register, but I don't understand it. I find the PPC register bits always being number backwards compared to normal confusing which then leads on to not understanding how to programme this register.

I've looked at the example code for a few processors, but they unhelpfully set wide open masks and receive identifier zero. It would be far more helpful if those piece of code used a non-zero message identifier and did programme some masks.

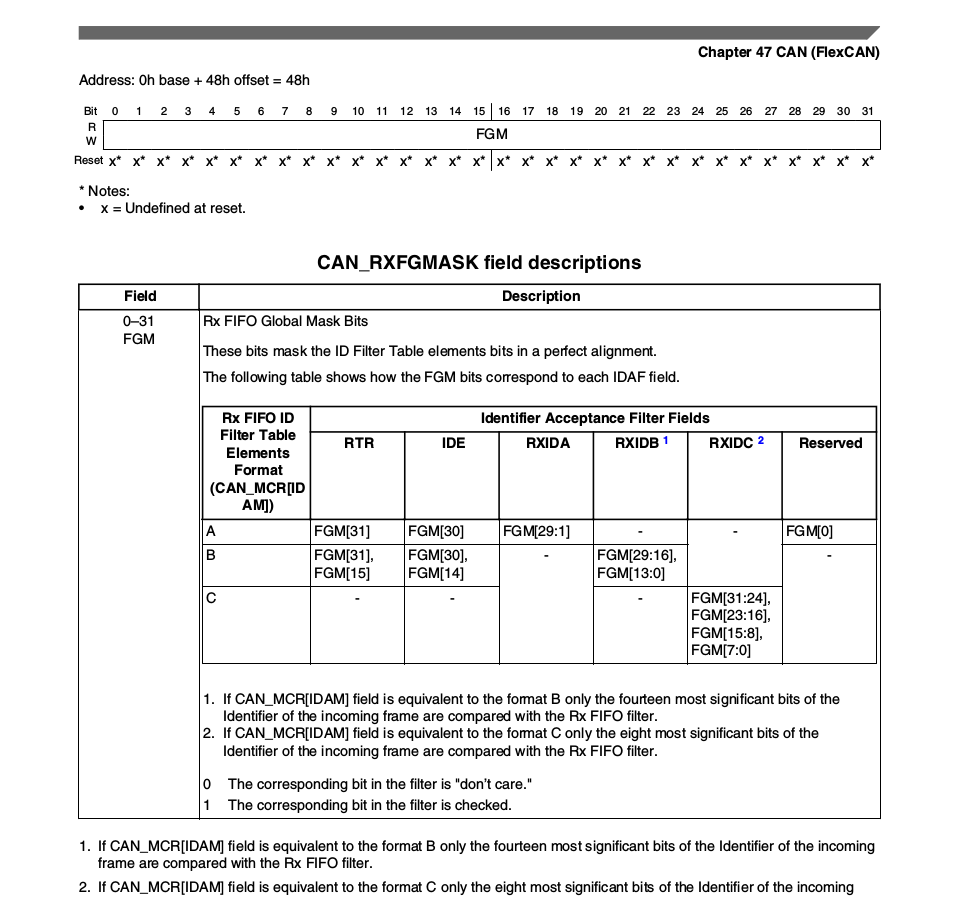

So.. this register's bits are numbered 0-31 for msb-lsb. I'm going to be using format 'A' with a single mask. The description table in section 47.4.17 lists:

RTR = FGM[31] <--- is this the msb or lsb ?

IDE = FGM[30]

RXIDA = FGM[29:1] <-- is this really 1:29 to match with the 'backwards' numbering or 29:1 to match normal numbering ?

Reserved = FGM[0] <-- is this the msb or lsb ?

It would be far more helpful (to me) to show the three Filter Table Elements Formats as three variants of the register description instead of using the table due to the ambiguity about bit numbering.

James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

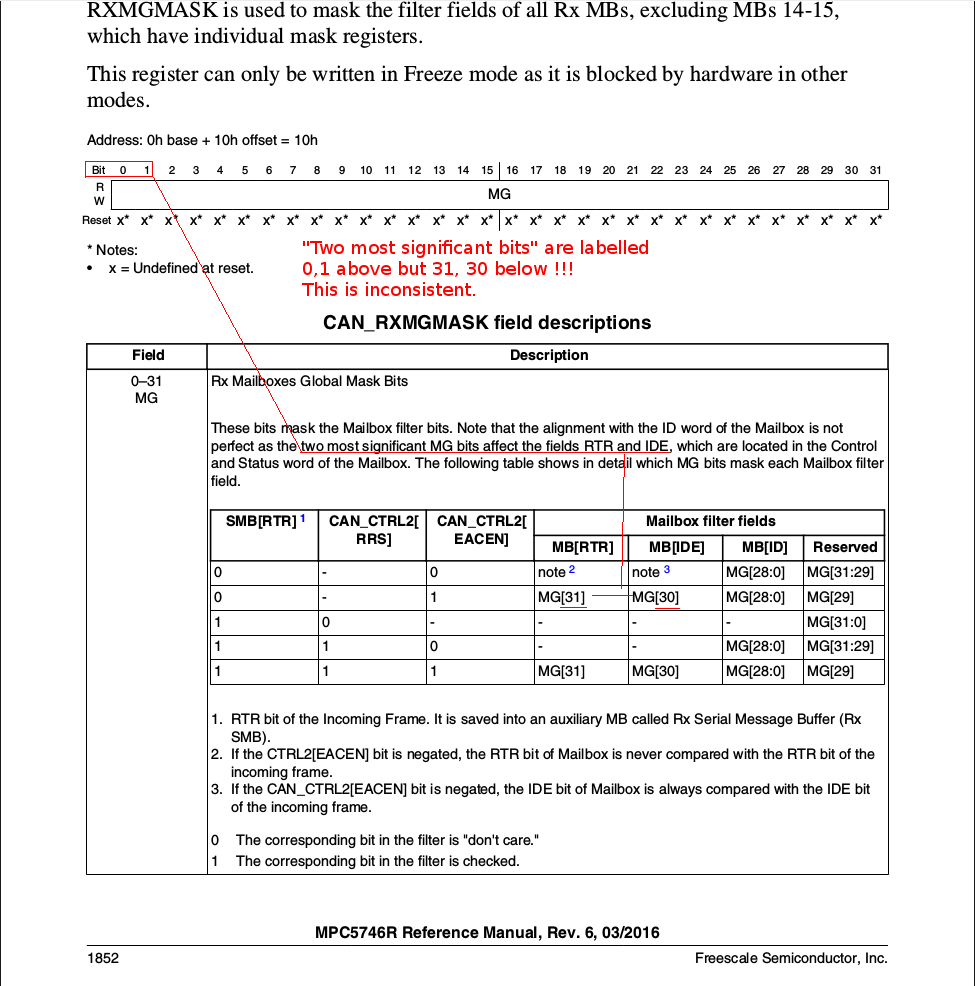

Slightly earlier in the manual in section 47.4.5 another register has conflicting information as below:

This mixing of bit numbering is not helpful. Please resolve it. As per my previous comment, showing the register pictorially for the five cases could aid clarity.

James

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi James,

yes, you are right. The bit alignment is not clear for those registers. The PowerPC notation is used for the registers, where 0 is MSB and 31 LSB. Sometimes bitfields use opposite direction in its description, but in this case the alignment should be clearly stated.

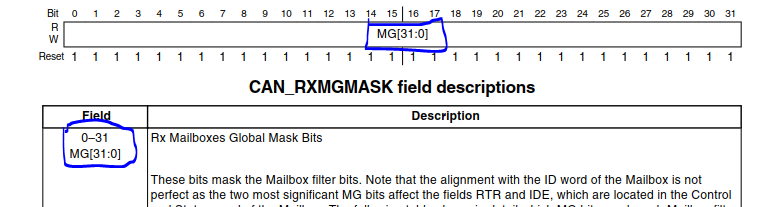

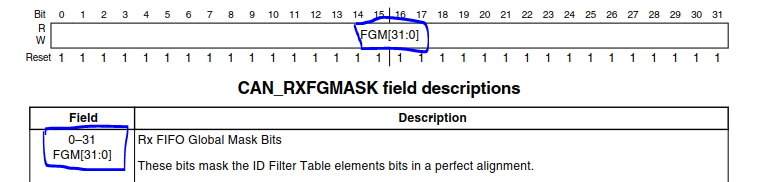

For example; same registers from MPC5744P RM

BR, Petr