- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

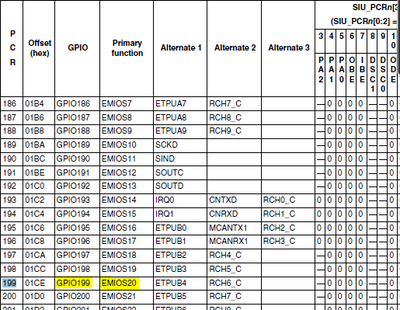

We are working on MPC5777C hardware and configured ICU(Input capture unit) module (GPIO199) for detecting falling edge triggering functionality.

The GPIO199 has primary functionality of EMIOS0_channel20 and same we want to use and expecting to trigger the interrupt for the same

This GPIO199 which is used as input is getting toggled and we have observed the same in GPDI199 register

For ICU module - we are USING SAIC mode and followed this sequence in init sequence

Icu_Init((Icu_ConfigType *)0);

Icu_EnableNotification(0);

Icu_EnableEdgeDetection(0);

please find below code modification done for EMIOS0_CH20-

During Initialisation -

SIU.IMUX5.B.MUXSEL4 = INPUT_MULTIPLEXING_SEL1; /*EMIOS_0 Ch20*/

SIU_PCR(199) = 0x0500;

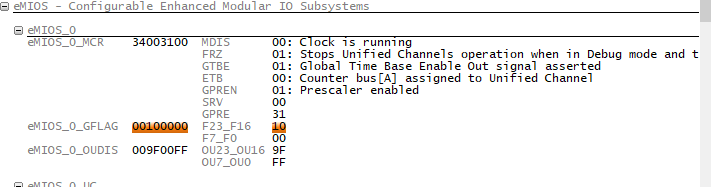

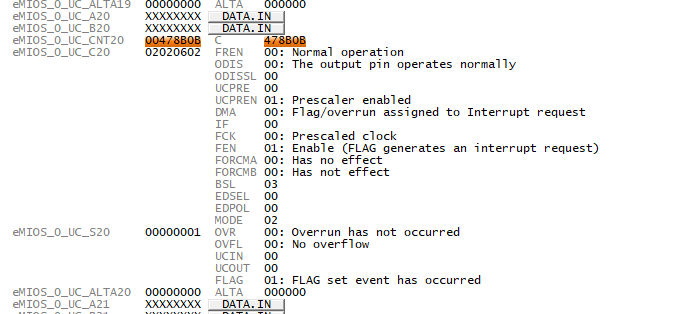

Below are peripheral registers related to EMIOS during freerun

As you could se FLAG for event is SET but still we are not getting expected interrupt.

Please let me know if any additional information is required.

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

be sure INTC module if properly initialized and check respective INTC_PSR (should be PSR206) if priority is set and request sent to right processor (PRC_SELn bits). Interrupt priority must be higher then current priority for given core (INTC_CPR_PRCn).

BR, Petr

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you Petr for your solution, Setting higher priority to INTC_PSR(206) resolved the issue.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

be sure INTC module if properly initialized and check respective INTC_PSR (should be PSR206) if priority is set and request sent to right processor (PRC_SELn bits). Interrupt priority must be higher then current priority for given core (INTC_CPR_PRCn).

BR, Petr