- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

-

- Home

- :

- MCUXpresso Software and Tools

- :

- MCUXpresso Config Tools

- :

- Re: LPC54113 CLK Generation

LPC54113 CLK Generation

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LPC54113 CLK Generation

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

i want to use an 10Mhz external clock from an Oszillator.

System clock shall be 120Mhz.

( by the way the data sheet says up to 150Mhz , manual UM10914 says 100Mhz )

I want to feed the flexcoms with the pll and not with the fro.

But i can't use the tool for that.

FRGCLKSEL to pll_clk will lead to the only option *256, which in my opinion is nonsense!

Error Message :

Issue: Output frequency must be lower than or equal to: 48 MHz

Level: Error

Type: Tool problem

Tool: Clocks

Origin: Clocks: BOARD_BootClockRUN

Resource: SYSCON.FRGCTRL_DIV

Information: Output frequency must be lower than or equal to: 48 MHz (See constraint 1)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi andreasruetten,

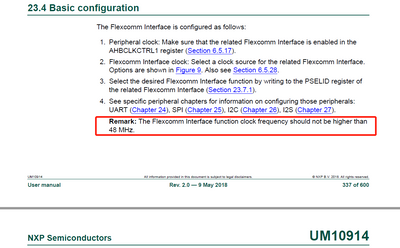

According to UM10914

"The Flexcomm Interface function clock frequency should not be higher than 48 MHz."

That's why we can't set Flexcom clock higher than 48Mhz in Configuration tool.

Thanks,

Jun Zhang

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

i don't want to set the freqency of the Flexcom clock higher than 48Mhz,

that was not my question!

I have an external 20Mhz input and 120Mhz Pll clock.

Please take a look on the picture i send!

My problem is the fixed *256 multiplicator in the tool.

Thanks Andreas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Andreas,

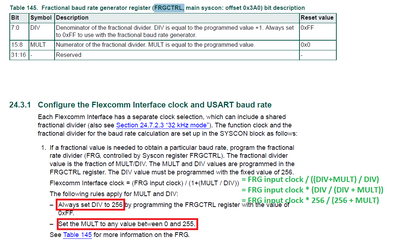

Let me explain the problem of the fractional divider of the LPC5411x MCU. The description of the functionality is little bit confusing in the user manual UM10914. You can find the following description of the FRGCTRL and also the functional description of Flexcomm fractional rate divider:

As you can see, when you transform the expression, there is fixed multiplicator 256 and divider with range 256 - 511. This is the functionality that is provided in this MCU.

I have checked the possibilities of the Flexcomm fractional divider and System PLL. If you need both the PLL output and main_clk to be 120 MHz the fractional divider cannot be used to divide the 120 MHz to 48 MHz (or lower). This combination of setting is not support on this MCU.

If you just need the PLL output 120 MHz and main_clk can use different clock source (for example the external clock source 20 MHz) the FRGCLKSEL can be use to select the main_clk and the fractional divider can be set to provide a requested frequency for the FLEXCOMM peripheral.

Best Regards,

Marek Neuzil

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Marek,

that does mean, that there is no possibility to power the core with 120Mhz and

an accuracy better than 1% ( with external source ) on flexcom interfaces ?

Our problem is that we need the processor power at high speed and accuracy better then 1%

Andreas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Andreas,

In this case you can also use the MCLKIN input (mclk_in clock source) for the Flexcomm interface. You can use for example the same external reference clock 20 MHz as it is used for the clk_in.

The mclk_in reference clock can be selected in FXCOMCLKSEL0 clock selector.

Best Regards,

Marek Neuzil

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Marek,

Data Sheet :

mclk_in The MCLK input function, when it is connected to a pin by selecting it in the IOCON block

Does this mean, that it could be any IO Pin ?

But i need 2 Pins, Right?

One mclk_in pin and one CLK_IN pin ...

Andreas

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Andreas,

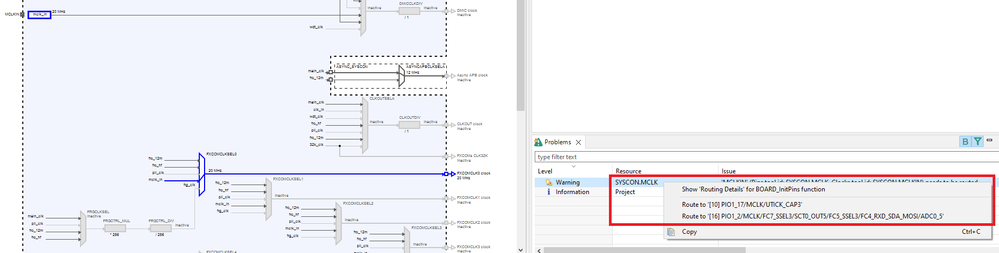

Yes, you need two input pins if you want to use the mclk_in as a reference clock source for the FLEXCOMM0 peripheral.

When you enable the mclk_in clock source the following warning is reported and you can use the context menu of the warning to route a pin for the mclk_in. The initialization code is provided (generated) in the Pins tool. You can select one of two routable pins for the mclk_in.

See the following screenshot:

Best Regards,

Marek Neuzil