- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- QorIQ Processing Platforms

- :

- Layerscape

- :

- USB3.0 Device Mode LS1021a

USB3.0 Device Mode LS1021a

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

USB3.0 Device Mode LS1021a

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have a ls1021a stand alone chip and type C male connector connects to the CPU, I want to plug this device into PC so my board can act like a device mode. What specifications I need to follow to make it work as device mode?

For example, is USB_ID pin from the CPU side I need to leave it as floating ?

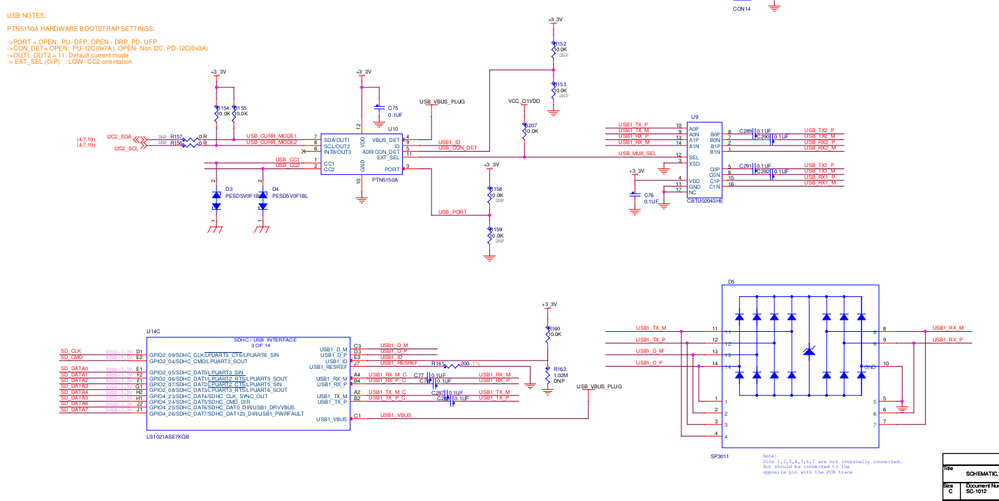

Below is my design:

can anyone tells me what is wrong here?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

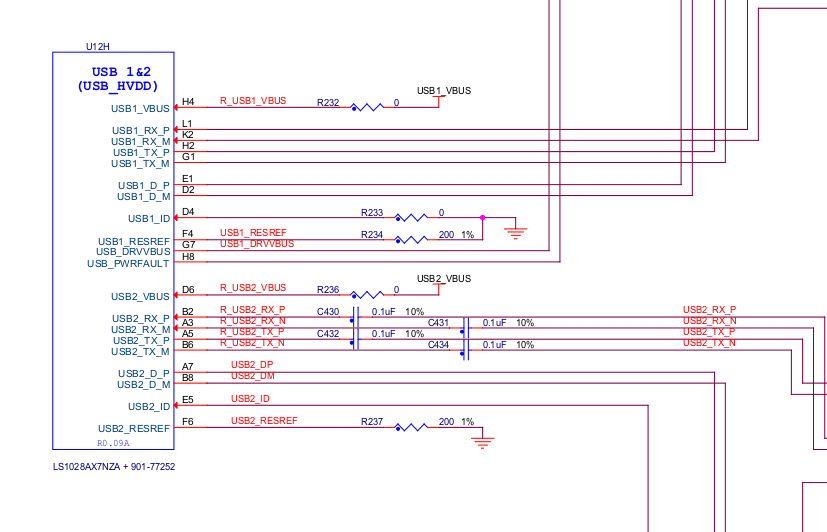

Please refer to the LS1028ARDB schematics page "28_LS10128 USB - TypeA & C" available at:

LS1028ARDB Development Board with high-speed interfaces and integrated TSN for Industrial IoT | NXP

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I know this document, my question is are type C and type A are handled differently?

Because in the page 28

USB1 (type A) and USB2 (type B) are designed differently.

If I use the type C design, can I plug into a Type A host using an USB adapter (Type C to Type A)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The connection schematics is incorrect in your case.

Please refer to the LS1028ARDB schematics page "28_LS10128 USB - TypeA & C" available at:

LS1028ARDB Development Board with high-speed interfaces and integrated TSN for Industrial IoT | NXP

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

sorry you replied too fast as I edit my post which part is wrong can you please highlight it ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Do you see that LS1028ARDB schematics page "28_LS10128 USB - TypeA & C" is not similar to yours?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I know it has both type A port and type C port but if I only have type C port and I want to plug into both type A host or type C host what is your recommendations ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We do not have such reference designs.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

ok let's focus on type C, I dont have CPLD in my case,

I have two scenarios.

(1) I removed the PTN5150A and there gonna be no CC1 and CC2, what pin strapping do I need for the USB_ID ? floating or pulled-up?

(2)I keep the PTN5150A what pin strapping do I need to for the USB_ID, CON_DET AND CC1 and CC2 to work as device mode ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

CPLD is not involved in the USB type C connection.

USB2_ID and USB2_BUFF_CON_DET are just shown in the USB_STAT register.

It is required to use PTN36043 and PTN5150A for the type C implementation.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

(1) what does this mean "

USB2_ID and USB2_BUFF_CON_DET are just shown in the USB_STAT register."

(2) If CPLD is not involved, what signals should I consider to handle the USB detection event( e.g. DRVVBUS should I make this as GPIO in the RCW so I can control it, if so how to control it ?, PWRFAULT do I need to consider this signal as well? if so how) because I found this thread answered by you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) Refer to the QorIQ LS1028A Reference Design Board Reference Manual, Rev. 1, 3.19 USB Control (USB_STAT).

2) Please refer to the AN4878 - QorIQ LS1021A Design Checklist.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

(1) How to read and write to this register? How to access this ?

(2) that is for 3.0 not type C

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) Do you have LS1028ARDB?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

no I dont, I only have ls1021a-TWR which I modified to device mode and it works

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The LS1021A-TWR has similar CPLD having memory-mapped registers accessed by means of IFC controller.