- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- QorIQ处理平台

- :

- Layerscape

- :

- Re: How Flash Timing Registers are configured for CPLD connectedon IFC Bus?

How Flash Timing Registers are configured for CPLD connectedon IFC Bus?

How Flash Timing Registers are configured for CPLD connectedon IFC Bus?

Hi,

We are having LS1021aTWR development board.

Below is the contents of ls1021atwr.h file(u-boot source code).

/* CPLD */

#define CONFIG_SYS_CPLD_BASE 0x7fb00000

#define CPLD_BASE_PHYS CONFIG_SYS_CPLD_BASE

#define CONFIG_SYS_FPGA_CSPR_EXT (0x0)

#define CONFIG_SYS_FPGA_CSPR (CSPR_PHYS_ADDR(CPLD_BASE_PHYS) | \

CSPR_PORT_SIZE_8 | \

CSPR_MSEL_GPCM | \

CSPR_V)

#define CONFIG_SYS_FPGA_AMASK IFC_AMASK(64 * 1024)

#define CONFIG_SYS_FPGA_CSOR (CSOR_NOR_ADM_SHIFT(4) | \

CSOR_NOR_NOR_MODE_AVD_NOR | \

CSOR_NOR_TRHZ_80)

/* CPLD Timing parameters for IFC GPCM */

#define CONFIG_SYS_FPGA_FTIM0 (FTIM0_GPCM_TACSE(0xf) | \

FTIM0_GPCM_TEADC(0xf) | \

FTIM0_GPCM_TEAHC(0xf))

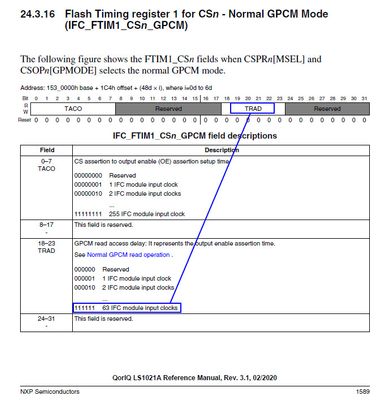

#define CONFIG_SYS_FPGA_FTIM1 (FTIM1_GPCM_TACO(0xff) | \

FTIM1_GPCM_TRAD(0x3f))

#define CONFIG_SYS_FPGA_FTIM2 (FTIM2_GPCM_TCS(0xf) | \

FTIM2_GPCM_TCH(0xf) | \

FTIM2_GPCM_TWP(0xff))

#define CONFIG_SYS_FPGA_FTIM3 0x0

How these CPLD timing parameters for IFC GPCM calculated?

I'm using ls1021atwr based custom board. Here SRAM(IS62WV25616EBLL) is connected on IFC bus in GPCM mode. In this case how to configure Flash timing register values for SRAM?

Thanks for your support.

Please refer to:

1) QorIQ LS1021A Reference Manual, 24.7.1.1.1 Normal GPCM internal counter-based program operation and 24.7.1.2.1 Normal GPCM internal counter-based read operation containing figures describing IFC timing parameters.

2) the SDRAM datasheet timings.

NOTE: IFC module input clock is equal to LS1021A Platform clock.

Considering above note calculate values of the IFC timing parameters to be in accordance with the SDRAM datasheet.