- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- LPCマイクロコントローラ

- :

- LPC5514 I2S SLAVE

LPC5514 I2S SLAVE

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

LPC5514 I2S SLAVE

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

LPC55S69 A I2S SLAVE --> LPC55S69 B I2S MASTER

LPC55S69 B as I2S master , provide MCLK. LRCK, BCLK to LPC55S69 A I2S SLAVE.

LPC55S69 A as I2S slave, provide audio data to LPC55S69 B I2S MASTER

how can I refer to which demo?

IF I2S slave want transmit audio data ,should put data to TXFIFO or RXFIFO?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

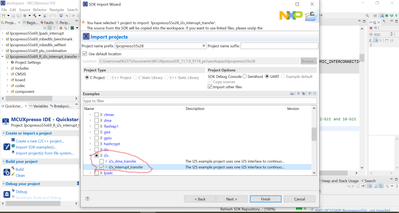

From your description, I see that you want to use two LPC5569-EVK boards to implement the I2S communication.

In the SDK package, there is I2S master example

For the I2S slave, you can develop the slave I2S example based on the master example.

static i2s_config_t s_RxConfig;

I2S_TxGetDefaultConfig(&s_RxConfig);

s_TxConfig.divider = DEMO_I2S_CLOCK_DIVIDER;

s_TxConfig.masterSlave = kI2S_MasterSlaveNormalSlave; //DEMO_I2S_TX_MODE;

I2S_TxInit(I2S6, &s_RxConfig);

In the slave mode, the SCK and WS for I2S6 will be input pins, you can assign the I2S6 pin in the pin_mux.c

Hope it can help you

BR

XiangJun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Can LPC support config I2S bitdepth?

I saw SDK support set I2S datelen and framelen only.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

what do you mean for the " I2S bitdepth"? do you mean that the WS occupies only one SCK cycle instead of 50% duty cycle? if it is the case, of course, it supports the WS occupies only one clock cycle of SCK.

As the following Fig, the WS width is controlled by MODE bits.

Hope it can help you

BR

XiangJun Rong

Hope it can help you

BR

XiangJun Rong