- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- Neural Processing UnitsNeural Processing Units

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

- Neural Processing Units

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Re: LPC4370 M0SUB core Jtag access accidentally disabled

LPC4370 M0SUB core Jtag access accidentally disabled

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I encountered the same problem as mentioned in this thread.

BUT I found something interesting. Hope someone can solve the problem.

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

According to this errata - 3.12 OTP.2, LPC4370 sometimes erroneously programs OTP memory. Some bits inside OTP will surely disable debug access to certain cores.

Should use special circuit to avoid this problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

According to this errata - 3.12 OTP.2, LPC4370 sometimes erroneously programs OTP memory. Some bits inside OTP will surely disable debug access to certain cores.

Should use special circuit to avoid this problem.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Zhengyang,

Do you modify the OTP area by yourself on our board?

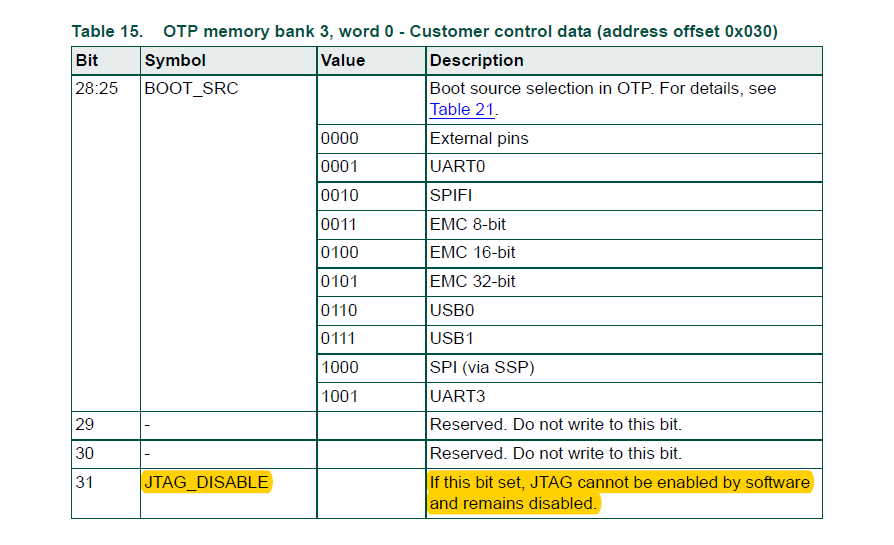

From your post information, your 0x40045030 is 0x20000080, is it LE mode or BE mode? If BE mode, your JTAG_DISABLE bit is set, then the JTAG cann't be enabled by software and remains disabled.

Do you configure the OTP area by yourself?

Besides, do you try to use the Cortex M4 to read it, is it the same result?

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your reply, Kerry.

Do you modify the OTP area by yourself on our board?

No, I was developing when finding M0SUB unaccessible.

is it LE mode?

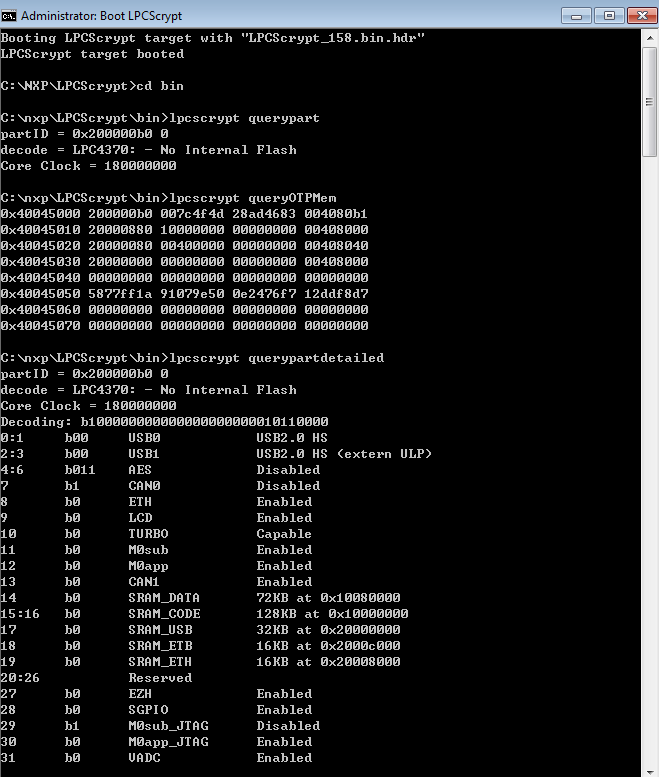

Yes, it's LE mode, but 0x20000080 = 0b0010'0000'0000'0000'0000'0000'1000'0000 , bit31 is not set. but reserved bit 29 is set.

Do you configure the OTP area by yourself?

No.

Besides, do you try to use the Cortex M4 to read it, is it the same result?

Yes, I got this result with LPCScrypt software provided by NXP.

Besides, I found CREG5 is 0xc0000660 after reset. Bit 10 M0SUBTAPSEL is always set.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Zhengyang Qu,

Thanks a lot for your updated information.

It's my mistake, yes, you are correct, if it is the LE mode, the JTAG_DISABLE bit is enabled.

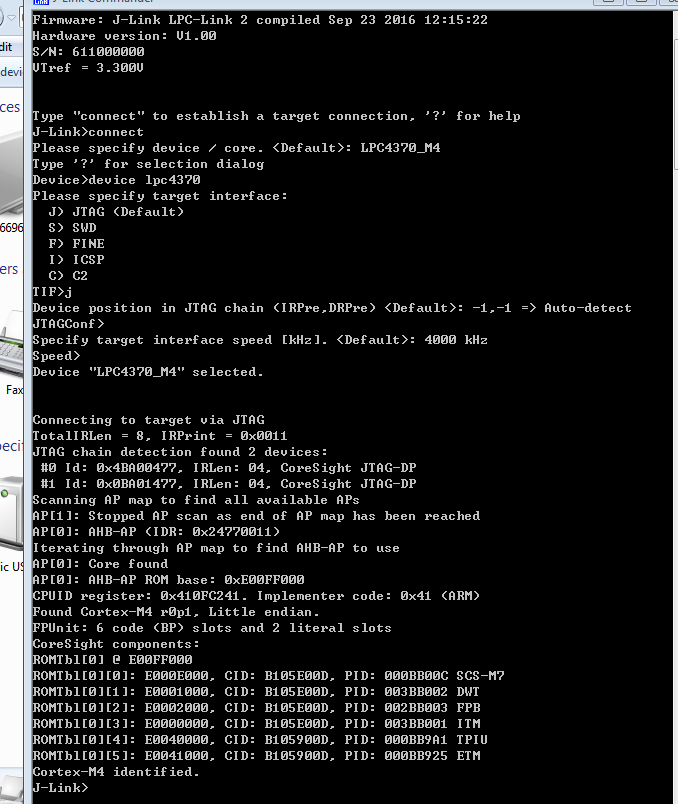

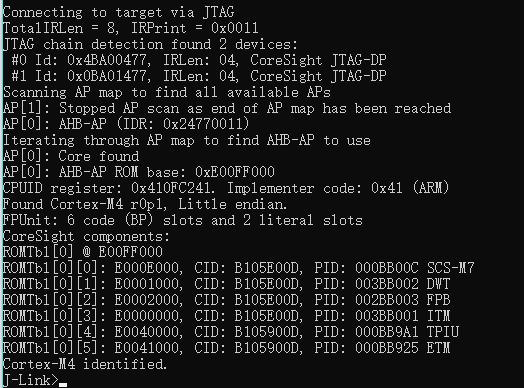

I also check the OTP memory, this is my LPC-LINK2 information:

Yes, your JTAG_DISABLE is still enabled, about the reserved bit, we can ignore the data.

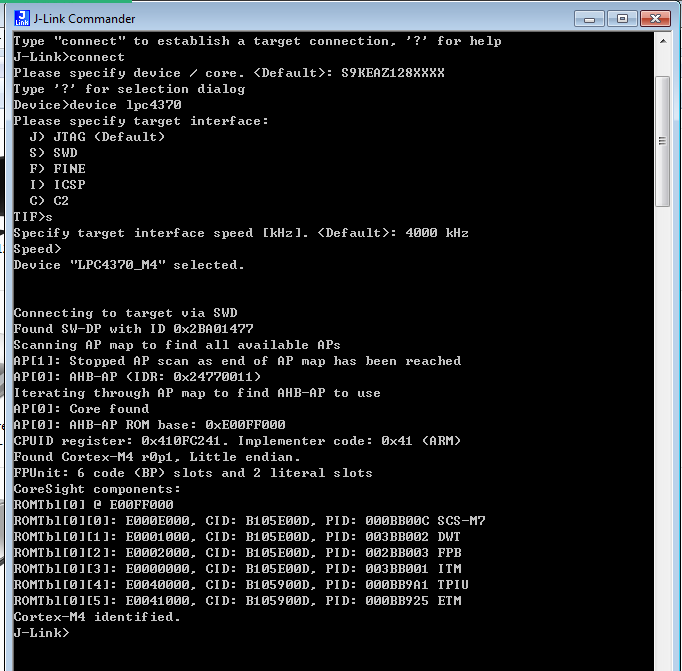

I have a question, if you the JLINK commander with SWD interface or JTAG interface, do you can connect your Cortext M4 core?

Have a great day,

Kerry

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

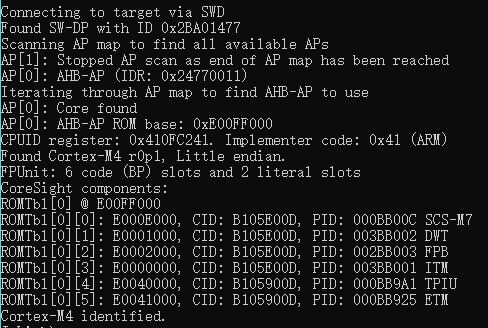

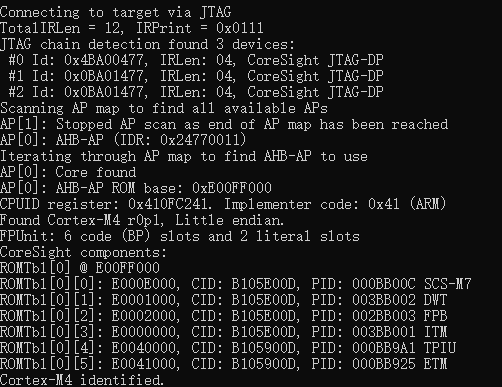

Thanks for your reply, Kerry.

This is my result.

I have M4 and M0APP cores access.

PS: On another board with M0SUB core access, the result shows 3 JTAG taps can be detected. I think your LINK2 may have the same problem.