- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

I2S channel swapping issue on LPC2470

Hi,

I’m currently working with a LPC2470 microcontroller and I have an issue with the I2S when used in 32 bit stereo mode. It is currently configured with DMA requests to copy the received I2S frames to memory. The LPC2470 is used as a slave on the I2S and the SCK (serial clock) and the WS (word select) are coming from another I2S peripheral. The WS is currently setup with an 8 kHz clock and the SCK is setup with a 256 kHz clock.

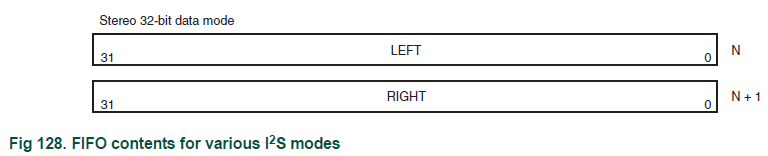

The issue is that I don’t have any way of knowing if the data the LPC2470 received on the I2S is starting with a LEFT I2S channel or a RIGHT I2S channel. Since the LPC2470 is an i2s slave, it seems the first channel received is dependent on when the i2s module is started. Sometimes the first channel is a left channel, and sometimes it is the right channel first. By looking at the user manual (UM10237 rev. 4) in the i2s chapter 23, it shows that the channel reception sequence ensure that a left channel will be followed by right channel as seen in the picture below.

However, nothing suggest that the first channel that the i2s will write in its RX FIFO buffer will be a left channel or am I missing something ? Is there a way to know which channel is received first without using a framing scheme ?

Kevin Landry

I see data_right and data_left enables which wsd is using is in wrong notation in receiver figure .

This enables must be exchanged because according to specification of I2S bus

The word select line indicates the channel being transmitted:

• WS = 0; channel 1 (left);

• WS = 1; channel 2 (right).