- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- General Purpose Microcontrollers

- :

- LPC Microcontrollers

- :

- Adding an interrupt handler for eeprom reads and writes

Adding an interrupt handler for eeprom reads and writes

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Adding an interrupt handler for eeprom reads and writes

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello!

I have now a working IAP EEPROM driver that works together with interrupts.

I had to move the interrupts vectors to address 0x10000000 into SRAM in order to make it work.

However, since reads and writes are hardware dependent,

I want to know when my read or write operation is done so that I can queue every interrupts and notice the processor.

Is there anyway to add an interrupt handler for the IAP eeprom library that is used?

An hard-fault will occur if I have a for loop and write to the IAP without any delay but if I add a delay of 1 ms things are fine (still testing will run it 1 day).

I want to have working writes and reads in the background (queue based) where an interrupt shall indicate when a write transaction is complete so that I do not write under a write transaction ( causing abnormal behavior such as hard faults and etc).

Is there anyway to add a custom made interrupt handler for this kind of problem ?

What is the way to go?

PS+

This is the continuation of the following problem in :

Is there any way to remove the interrupt handling in the IAP eeprom for LCP11XX

The goal is to have an interrupt handler for the EEPROM indicating when a write or read is done:

Here is an example code:

/* EEPROM interrupt handler */

void eeprom_interrupt_in_bgo()

{

interrupt_que_eepromWrite()

interrupt_que_eepromRead()

// when done issue next write or read in order to synch writes

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello again jeremyzhou

Ah ok.

Thanks for the answer I guess I have to look for other solutions then.

Apart from the current solution, will NXP come up with a more robust solution in order to handle time critical applications for future processors?

We are in need of an EEPROM driver that shall work without disabling or enabling the interrupts.

I have also seen some legacy solution where a ".a" is provided, thus, working without interrupt handling.

regards,

Volkan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Volkan Coskun,

Thanks for your reply.

1) Apart from the current solution, will NXP come up with a more robust solution in order to handle time-critical applications for future processors?

-- As I know, there's no similar plan, however, I'll contact the AE team to confirm it.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

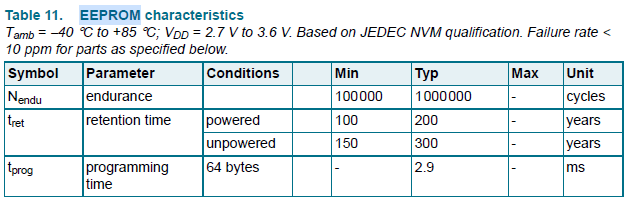

Also, how long does it takes for reads and writes when using EEPROM.

I could not really find it in the datasheets while I was looking.

regards,

Volkan Coskun

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Thank you for your interest in NXP Semiconductor products and for the opportunity to serve you.

1) Is there any way to add an interrupt handler for the IAP EEPROM library that is used?

-- No, I'm afraid not, in addition, there's a suggestion below from the AN11511.

During EEPROM write and read operations, the interrupts must be disabled for proper IAP operation.

2) The dynamic characteristics of the EEPROM.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Aha ok,

I am still a little bit confused here.

What was the purpose of moving the interrupt vectors from 0x00000000 to 0x10000000?

I thought the reason why we had to move the interrupt vectors was simple because to enable interrupts during EEPROM write/read transactions, and thus, letting other interrupts run without intervening them , i.e., disable or enable.

Is there any other alternative for EEPROM ?

To sum it up,

it is not possible to use the EEPROM IAP or any other library with interrupts enabled, and, this is also true for when we move the interrupt vectors or let them be as it is.

Have I understood the manual and the IAP eeprom library correctly ?

regards,

Volkan Coskun

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Volkan Coskun,

Thanks for your reply.

1) Have I understood the manual and the IAP EEPROM library correctly?

-- In general, you're correct. The interrupt vector remap can allow the interrupts to occur even during the IAP routines are used except for EEPROM to write and read operations.

Have a great day,

TIC

-------------------------------------------------------------------------------

Note:

- If this post answers your question, please click the "Mark Correct" button. Thank you!

- We are following threads for 7 weeks after the last post, later replies are ignored

Please open a new thread and refer to the closed one, if you have a related question at a later point in time.

-------------------------------------------------------------------------------