- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- MCUXpressoソフトウェアとツール

- :

- Kinetisソフトウェア開発キット

- :

- Setting FBI mode with SDK

Setting FBI mode with SDK

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Good morning

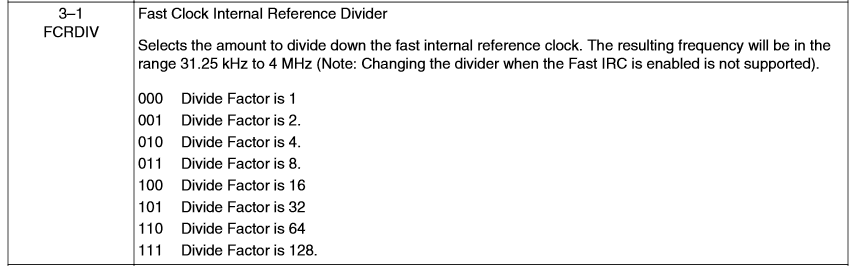

I try to execute this call with different values of fcrdivVal, the fourth parameters in the function.

CLOCK_HAL_SetFbiMode(MCG_BASE, kMcgDcoRangeSelMid, kMcgInternalRefClkSelFast, 5, CLOCK_FllStableDelay, &outClkFreq );

It execute correctly with values from 0 to 5. The clock is 125 KHz with a value of 5.

If the fcrdivVal is 6 the clock is updated (32KHz), I see on the scope as CLOCKOUT, but the debugger looses the control.

Is it normal???

Solutions???

Thank You

解決済! 解決策の投稿を見る。

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Pietro,

Why do you change the divider when you use the FBI?

If you go to Reference Manual, page 593

http://cache.freescale.com/files/microcontrollers/doc/ref_manual/K64P144M120SF5RM.pdf

so, the value for fcrdivVal = 6, output frequency cannot be 32KHz.

Because when the value is 5, 4MHz and Divide Factor is 32, is 125KHz. It is right.

BUT: when is the value 6, 4MHz and Divide Factor is 64, it is 62,5KHz, not 32KHz.

(4MHz : 64 = 62,5KHz)

As it is written in the Reference Manual : you have not change the divider when the Fast IRC is enabled.

Please, look to SIM Module, Register SIM_CLKDIV1->OUTDIV4 what is your frequency divider for flash memory.

Best Regards,

Iva

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi ..

I am still interested in some assistance.

Thank You

Pietro

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Pietro,

Why do you change the divider when you use the FBI?

If you go to Reference Manual, page 593

http://cache.freescale.com/files/microcontrollers/doc/ref_manual/K64P144M120SF5RM.pdf

so, the value for fcrdivVal = 6, output frequency cannot be 32KHz.

Because when the value is 5, 4MHz and Divide Factor is 32, is 125KHz. It is right.

BUT: when is the value 6, 4MHz and Divide Factor is 64, it is 62,5KHz, not 32KHz.

(4MHz : 64 = 62,5KHz)

As it is written in the Reference Manual : you have not change the divider when the Fast IRC is enabled.

Please, look to SIM Module, Register SIM_CLKDIV1->OUTDIV4 what is your frequency divider for flash memory.

Best Regards,

Iva

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Iva

Yes I should not divide in such condition. That's a good point.

Thank You

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Iva

Sorry. I will detail..

KDS Version: 2.0.0

SDK 1.1.0

Thank You

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi, Pietro,

Can you tell me the part number of the Kinetis and the version of SDK?

BR

XiangJun Rong

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank You for assistance

I am using the FRDM K64. I am debugging with the JTAG, in reduced version with only the two pins, as in the schematic.

I use the KDS.

I am suspicious the slow clock is not handled in this reduced JTAG connection...

Let me know

Best Regards

Pietro di Castri

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Pietro,

like Rong said, we need exact information about versions, which you use.

KDS is IDE, Kinetis Design Studio and KSDK is Kinetis Software Development Kit.

You can find it on C:\Freescale and folders KDS_2.0.0 and KSDK_1.1.0.

Iva