- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- MCUXpresso软件和工具

- :

- Kinetis软件开发套件

- :

- SPI sck strange behavior

SPI sck strange behavior

Hello Freescale community,

I use Kinetis Design studio 2.0.0, MQX KSDK 1.0.0 with Processor expert, (uc MK64F),

I realized SPI communication using SPI0 and two channels DMA for Tx et Rx. I talk with a multiports (ADC,DAC, GPI,GPO) component at 4MHz.

I chose sck non-continuous for the configuration of the SPI

The frame format is 3 bytes : One for CMD, one for data LSB and one for data MSB.

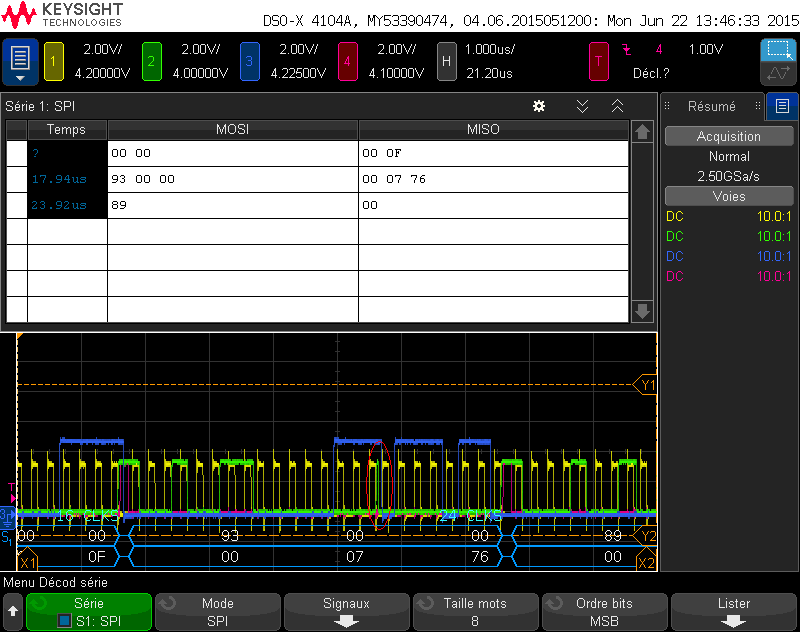

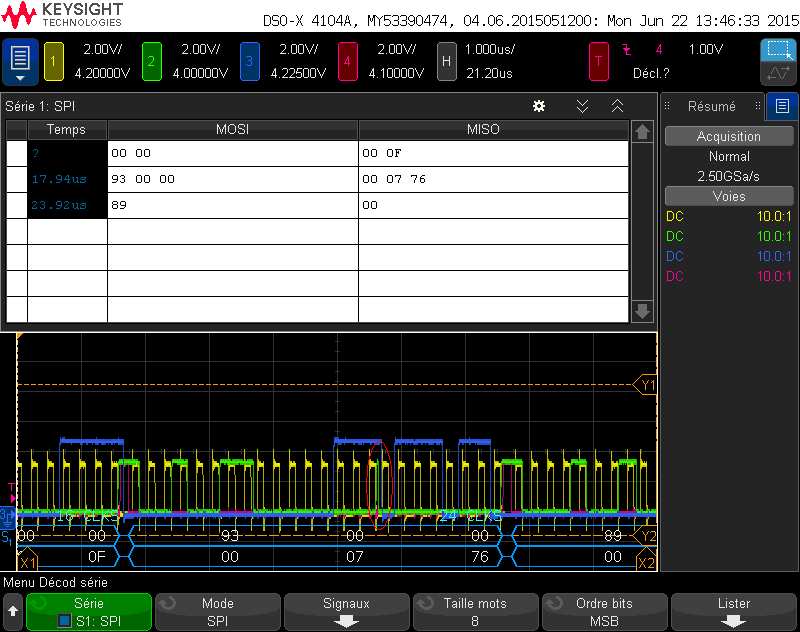

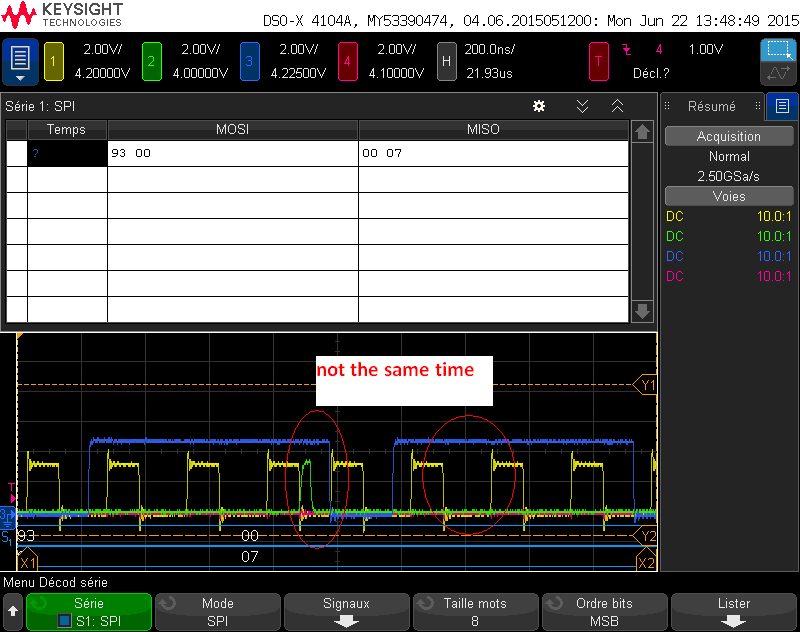

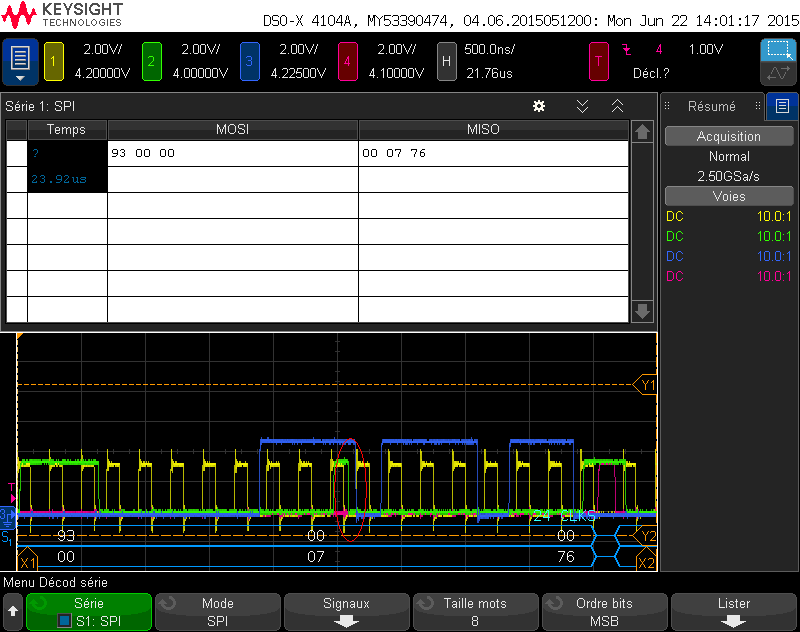

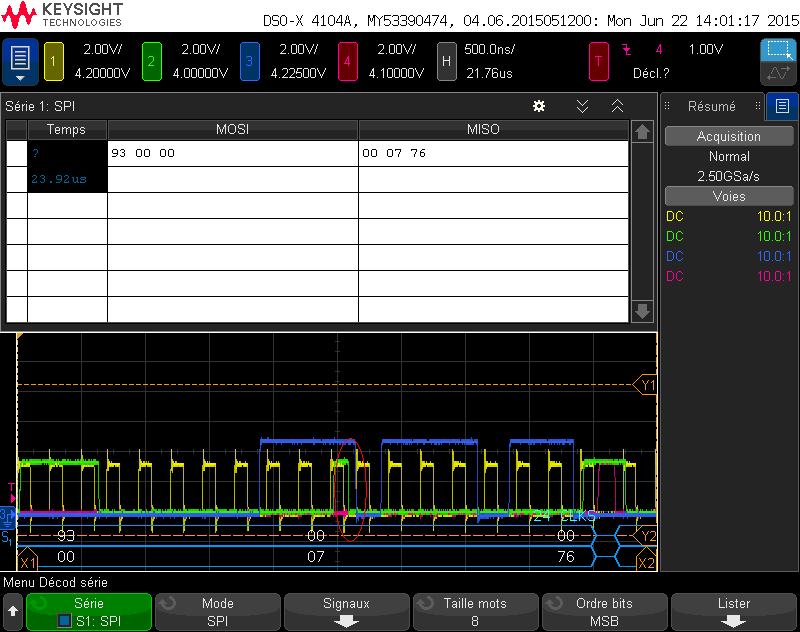

I have a problem with reception of the first bit of each new byte because the sck signal has a strange behavior : the gap between two clock cycle is good but the gap between the 8th bit and the first bit of the next byte is different. You can see the behavior on the following screenshot :

with a zoom we can very well if the clock difference :

What the problem, Can you help me ?

I'am not interresting to use sck continuous mode,

I have found a solution for not having problem reading the first bit of new byte using functions :

static inline void DSPI_HAL_SetModifiedTimingFormatCmd(uint32_t baseAddr, bool enable)

and

static inline void DSPI_HAL_SetDatainSamplepointMode(uint32_t baseAddr,dspi_master_sample_point_t samplePnt) with "kDspiSckToSin_1Clock"

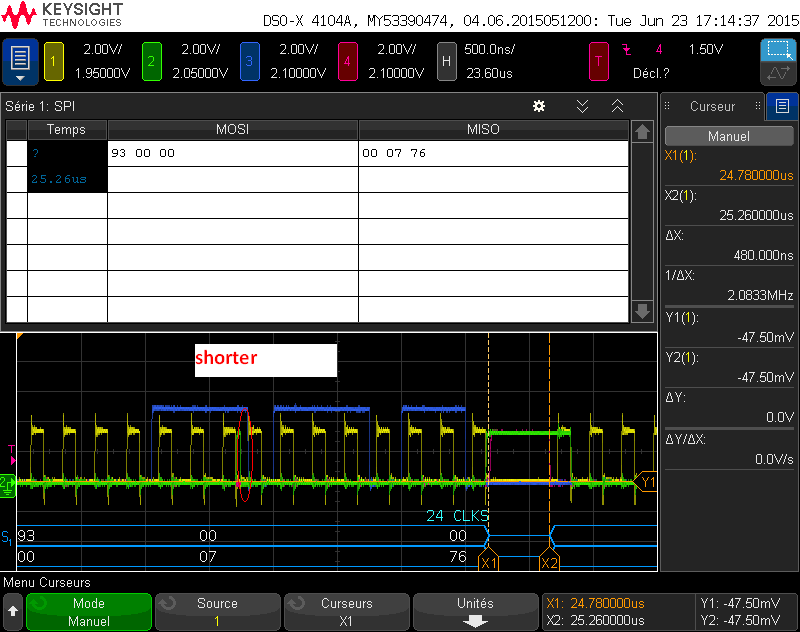

But signal MOSI is modify and I think this is not a properly operation

You can see with this modifications :

Please can you give me some advices to resolve this problem ?

已解决! 转到解答。

Hello,

Hello PE TAPIE:

If I understand correctly the time between frames is shorter than the time between bits, right?

You can try setting a delay with the API DSPI_DRV_MasterSetDelay(instance, kDspiAfterTransfer, [nanoseconds], & calculatedDelayaftertransfer). In nanoseconds you would set the time to match the time you get between bits.

I hope this helps!

Regards!,

Jorge Gonzalez

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hello Jorge Gonzalez,

Thanks for your answer,

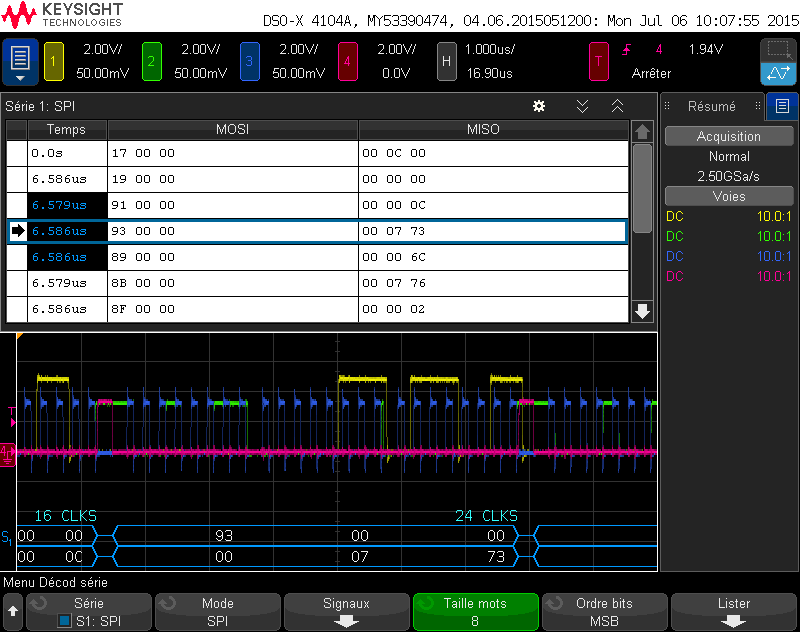

I have already use this function for apply special delay, but the delay "kDspiAfterTransfer" allow to modify the delays between two activation of the chip select and not between the 8th bit and the first bit of the next byte.

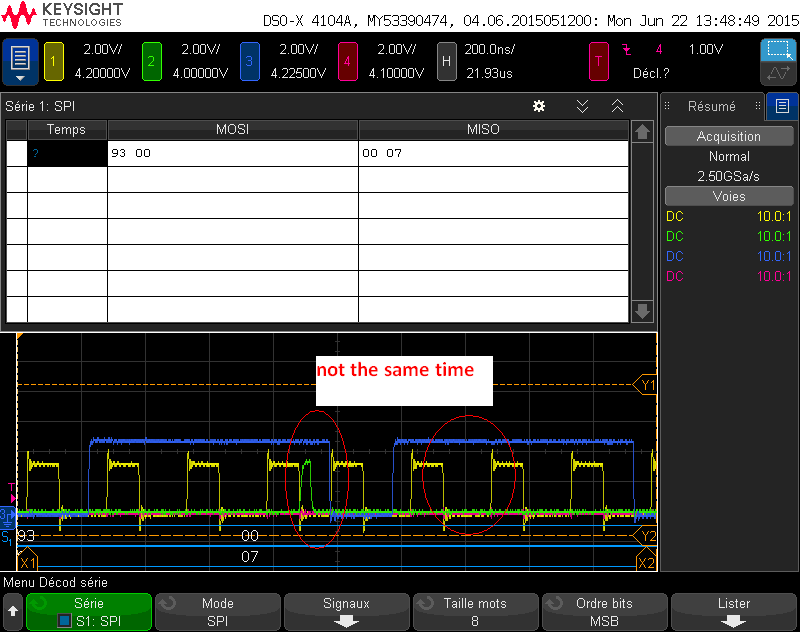

In this image you can see the delay of 400 ns I apply :

But my problem is still present,