- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- MCUXpresso Training Hub

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

-

- Home

- :

- 通用微控制器

- :

- Kinetis微控制器

- :

- Which DRAM controller slave ports is able to be accessed through which master ports on a Kinetis K70

Which DRAM controller slave ports is able to be accessed through which master ports on a Kinetis K70

I am doing an application where performance is extremely important, causing the need for pushing the K70 to its performance limits. One of the requirements is that I need to DMA data with approximate 50 MB/s from the Flexbus to DDR memory with very low latency, while the Cortex-M4 also accessing the memory controller.

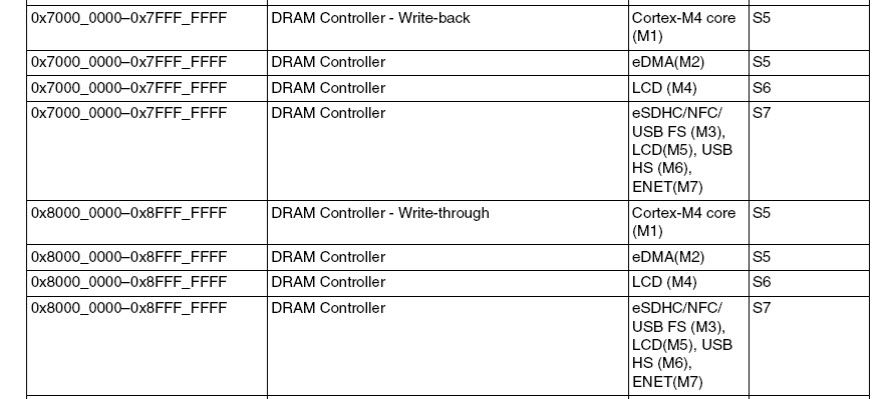

According to the K70 reference manual the DRAM controller’s slave ports can be accessed by the following master ports based on address range.

0x7000_0000-0x7FFF_FFFF

- Cortex-M4 (M1), eDMA ( M2) can access S5, S6 and S7

- LCD (M4) can access S5, S6 and S7

- LCD (M5), eSDHC/NFC (M3), ENET (M7), USB (M6) can access S5

0x8000_0000-0x8FFF_FFFF

- Cortex-M4 (M1), eDMA ( M2) can access S5

- LCD (M4) can access S5, S6 and S7

- LCD (M5), eSDHC/NFC (M3), ENET (M7), USB (M6) can access S5, S6 and S7

Though looking in the Freescale training material http://www.freescale.com/files/training_pdf/WBNR_LA2012_K70SP.pdf?lang_cd=en page 27 it states:

0x7000_0000-0x7FFF_FFFF

- Cortex-M4 (M1), eDMA ( M2) can access S5

- LCD (M4) can access S6

- LCD (M5), eSDHC/NFC (M3), ENET (M7), USB (M6) can access S7

0x8000_0000-0x8FFF_FFFF

- Cortex-M4 (M1), eDMA ( M2) can access S5

- LCD (M4) can access S6

- LCD (M5), eSDHC/NFC (M3), ENET (M7), USB (M6) can access S7

So what is correct? Is the Cortex M and DMA limited to one slave port together, or is the reference manual correct?

If the reference manual is correct. How can I change which slave port a master ports tries with its first attempt. I want to setup the system so the Cortex-M4 always asks S6 first, and the DMA always ask S7, and they both have the highest priority on those ports. The LCD is then able to share the last port together with the USB, ENET etc.

I know about the port priority (AXBS_PRSn), and arbitration (AXBS_CRSn) registers, but I can not find any details above the other elements, which I need to know to push the K70 to it full potential.

Notice, I have created a service request about this issue (1-3027240671 ) and will try to update this thread if possible with information I receive.

已解决! 转到解答。

Hi Claus,

Please check below K70 updated DRAM controller memory map info.

Related info will be updated at next version K70 reference manual soon.

Sorry for our document with incorrect info may bring any inconvenience to you.

Wish it helps.

best regards

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Hi Claus,

Please check below K70 updated DRAM controller memory map info.

Related info will be updated at next version K70 reference manual soon.

Sorry for our document with incorrect info may bring any inconvenience to you.

Wish it helps.

best regards

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

Thanks for the update.

Just for other users running into the same issues.

Based on your answer it seems that the optimum settings is something like.

| Slave port | Prio1 | Prio2 | Prio3 |

|---|---|---|---|

| S4 | M2 | M1 | Don't care |

| S5 | M2 | M1 | M0 |

| S6 | M4 | Don't care | Don't care |

| S7 | M5 | M3 | M6 |

And regarding parking register, something like.

| Slave port | Parked |

|---|---|

| S4 | M2 |

| S5 | M2 |

| S6 | M4 |

| S7 | M5 |

I am looking into the DDR controller registers for the last performance tweaks.

Have a nice day.

Hi Claus,

I am in processing to get confirmation info from Kinetis product team.

Thank you for the patience.

Wish it helps.

best regards

Ma Hui

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------