- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- SPI last bit on every byte is high

SPI last bit on every byte is high

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

SPI last bit on every byte is high

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi!

We see that the last bit in every Byte transmission on MOSI is set to high. We are using the SPI with DMA

If I read the registers of the SPI after the configuration I get:

- MCR 0x883F0000

- TCR 0x00000000

- CTAR 0x3E050004

- CTAR 0x78000000

- SR 0x42000000

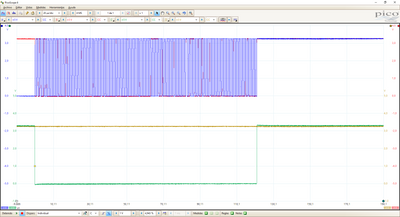

If we connect the oscilloscope to the SPI lines we see the next:

Blue -> SCK

Red -> MOSI

Green -> /CS

Yellow -> /RESET (device reset)

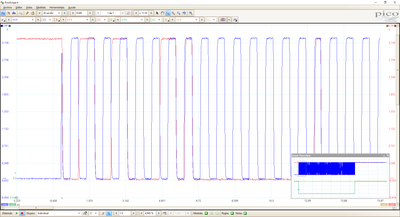

If we zoom on the MOSI and SCK lines we see the issue. This 2 bytes that can be seen in the capture are 0x52 and 0x00. You can see how the last bit goes high in both bytes.

Does anyone know why this could be happening?

Regards,

Iñaki

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you so much for using our community. I really appreciate it.

I would like to help you in a proper way, so do you think may you share with me which part number you are using for? And then, may you tell me which devices you are trying to communicate via SPI ? Because those last 2 bytes does not make a lot of sense to me, but I would like to have more info to gladly help you of course.

I will stay tuned to your answer, so please let me know if you have more questions.

Thank you.

Best Regards.

Pablo Avalos.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

It is my pleasure to help you.

After checking what you are using for, it is unclear to me why it is happening to you those events at the end on the SPI frame. My suggestion is to check that your ADC chip is well connected and works correctly with the SPI clock from the MK24. After that, please download our SDK examples for TWR-K24 and try to run an example of dspi_interrupt_b2b_transfer_master with your ADC chip connected properly, and see if everything is ok.

Hope this steps might be helpful for you. Please let me know if you have more questions.

Best Regards.

Pablo Avalos.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

We have tested with the MOSI line disconnected in the ADC and the we see the same behaviour.

We are able to communicate with the ADC the most of the times, but there are other times that the data we receive from it does not make sense.

Thanks for you help.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thank you so much for your reply and thanks a lot for your patience.

So, do you think is there anything else I can help you with? Because if communication with ADC works perfectly most of the times, what do you think is happening when it does not works fine? I am running out of ideas what could be the problem there with that intermittency.

Please let me know if you have more questions, otherwise, please mark this answer as solution.

Thank you so much.

Best Regards.

Pablo Avalos.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Thanks for all your help, but It seems that the error with the ADC is not related to the SPI communication. We thought that as we saw that extrange behaviour on the SPI.

Regards,

Iñaki