- Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- Wireless ConnectivityWireless Connectivity

- RFID / NFCRFID / NFC

- Advanced AnalogAdvanced Analog

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

- S32M

- S32Z/E

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

- Generative AI & LLMs

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Knowledge Bases

- ARM Microcontrollers

- i.MX Processors

- Identification and Security

- Model-Based Design Toolbox (MBDT)

- QorIQ Processing Platforms

- S32 Automotive Processing Platform

- Wireless Connectivity

- CodeWarrior

- MCUXpresso Suite of Software and Tools

- MQX Software Solutions

- RFID / NFC

- Advanced Analog

-

- NXP Tech Blogs

- Home

- :

- 汎用マイクロコントローラ

- :

- Kinetisマイクロコントローラ

- :

- MKL14 - Problem changing system clock.

MKL14 - Problem changing system clock.

- RSS フィードを購読する

- トピックを新着としてマーク

- トピックを既読としてマーク

- このトピックを現在のユーザーにフロートします

- ブックマーク

- 購読

- ミュート

- 印刷用ページ

MKL14 - Problem changing system clock.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

On POR, I'm setting the system clock (MCGOUTCLK) to be the 4MHz High Speed Internal Reference clock. (ie. FBI mode with 4 MHz irc clock)

Using the following code:

-----------------------------------------------------------------

MCG_SC = 0;

MCG_C1 = MCG_C1_IREFS_MASK|MCG_C1_IRCLKEN_MASK;

MCG_C1 |= (1 << MCG_C1_CLKS_SHIFT);

while(MCG_S & (MCG_S_CLKST_MASK|MCG_S_IREFST_MASK) != (MCG_S_CLKST_MASK|MCG_S_IREFST_MASK));

MCG_C2 = MCG_C2_IRCS_MASK;

while((MCG_S & MCG_S_IRCST_MASK) != MCG_S_IRCST_MASK);

-----------------------------------------------------------------

Most of the time this is working. But sometimes, on POR, the frequency is much faster. It's like the POR default clock (20.9 MHz) is still set.

I'm working on trying to get the system clock output so I can see the frequency when it fails.

Is there something I'm missing? Is there some other status bit I need to be checking?

Thanks.

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Brian

Is this specific to POR or after every reset (watchdogs, external, etc.)? Usually the clock is configured after all reset types.

In the uTasker project one selects this clock mode with the define RUN_FROM_LIRC

The following code is then used:

MCG_SC = MCG_SC_FCRDIV_1; // no divide after fast clock (4MHz)

MCG_C2 |= MCG_C2_IRCS; // select fast internal reference clock (rather than slow one) for MCGIRCLK

MCG_C1 = (MCG_C1_IREFSTEN | MCG_C1_IRCLKEN | MCG_C1_CLKS_INTERN_CLK);// enable and select 4MHz IRC clock source and allow it to continue operating in STOP mode

while ((MCG_S & MCG_S_CLKST_MASK) != MCG_S_CLKST_INTERN_CLK) { // wait until the 4MHz IRC source is selected

}

SIM_CLKDIV1 = (((SYSTEM_CLOCK_DIVIDE - 1) << 28) | ((BUS_CLOCK_DIVIDE - 1) << 16)); // set system and bus clock dividers

MCG_C2 |= MCG_C2_LP; // disable FLL in bypass modeRegards

Mark

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

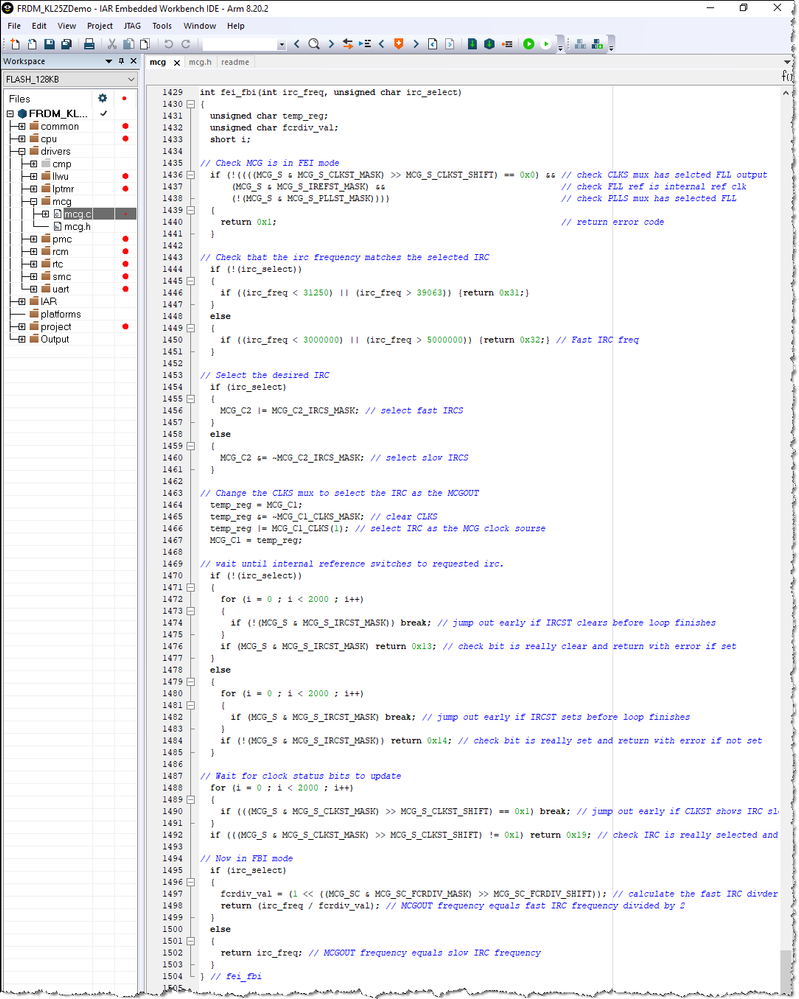

Hi Brian,

Please refer the fei_fbi() function in mcg.c file. This file can be found in KL25_SC.exe.(...\KL25 Sample Code\kl25_sc_rev10\klxx-sc-baremetal\src\drivers\mcg)

I have also attached the mcg files here.

SIM_SOPT2[CLKOUTSEL] can be use to output internal clocks, you can select Bus clock output on the CLKOUT (PTC3) pin.

Best Regards,

Robin

-----------------------------------------------------------------------------------------------------------------------

Note: If this post answers your question, please click the Correct Answer button. Thank you!

-----------------------------------------------------------------------------------------------------------------------

![SIM_SOPT2[CLKOUTSEL].png SIM_SOPT2[CLKOUTSEL].png](/t5/image/serverpage/image-id/62532i08936921AC75F4DA/image-size/large?v=v2&px=999)